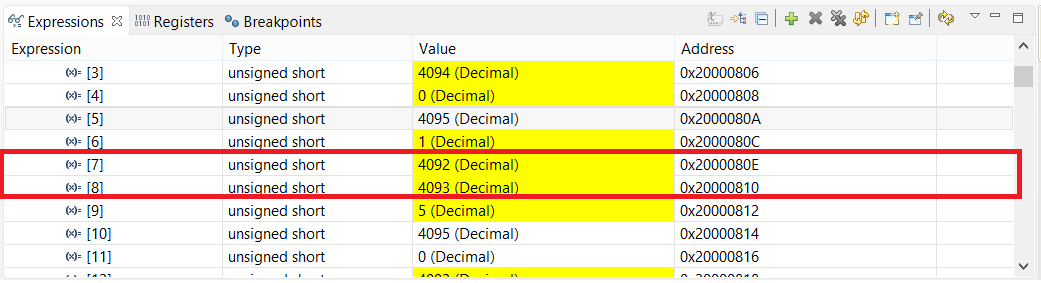

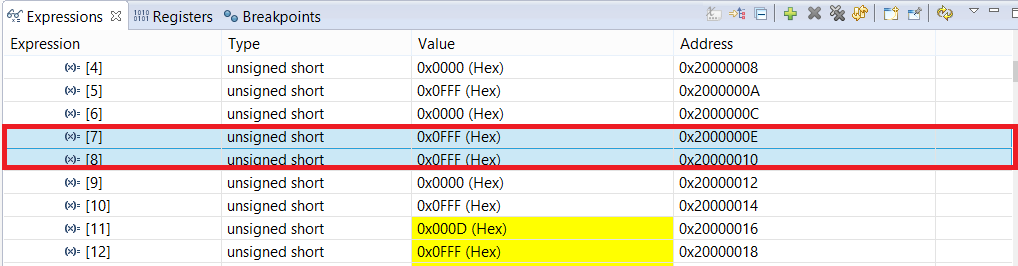

Hello everyone, I have configured ADC 0 to read two ADC channels (ADC_CTL_CH0 and ADC_CTL_CH1), one connected to 3.3V and onother connected to GND, I store this information in two buffers using uDMA in ping pong mode. The problem is that in the fourth transfer I get this:

As you can see, the ninth sample "[8]" of this ping pong DMA buffer is not the correct value that should be readed, It is suppose that I should get a low voltage value. I have configure ADC with DMA like this:

void ADCconfigure(uint32_t sysclock)

{

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOE); //Habilita puerto E

SysCtlPeripheralEnable(SYSCTL_PERIPH_ADC0);

GPIOPinTypeADC(GPIO_PORTE_BASE, GPIO_PIN_3|GPIO_PIN_2|GPIO_PIN_1); //PE3 PE2 PE1 tipo ADC

SysCtlPeripheralSleepEnable(SYSCTL_PERIPH_ADC0);

ADCClockConfigSet(ADC0_BASE,ADC_CLOCK_SRC_PIOSC | ADC_CLOCK_RATE_FULL, 1); //Clock source (Precision Internal Clock)

// ADCClockConfigSet(ADC0_BASE, ADC_CLOCK_SRC_PLL | ADC_CLOCK_RATE_FULL, 30);

ADCSequenceConfigure(ADC0_BASE, 0 , ADC_TRIGGER_ALWAYS, 3); // SS0-SS3 priorities must always be different

ADCSequenceStepConfigure(ADC0_BASE, 0 , 0, ADC_CTL_CH0); // ADC_CTL_TS = read temp sensor

ADCSequenceStepConfigure(ADC0_BASE, 0 , 1, ADC_CTL_CH1);

ADCSequenceStepConfigure(ADC0_BASE, 0 , 2, ADC_CTL_CH0);

ADCSequenceStepConfigure(ADC0_BASE, 0 , 3, ADC_CTL_CH1);

ADCSequenceStepConfigure(ADC0_BASE, 0 , 4, ADC_CTL_CH0);

ADCSequenceStepConfigure(ADC0_BASE, 0 , 5, ADC_CTL_CH1);

ADCSequenceStepConfigure(ADC0_BASE, 0 , 6, ADC_CTL_CH0);

ADCSequenceStepConfigure(ADC0_BASE, 0 , 7, ADC_CTL_CH1 | ADC_CTL_END | ADC_CTL_IE); // ADC_CTL_IE fires every 8 samples

ADCSequenceEnable(ADC0_BASE, 0);

ADCSequenceDMAEnable(ADC0_BASE, 0);

uDMAChannelAttributeDisable(UDMA_CHANNEL_ADC0,

UDMA_ATTR_ALTSELECT | UDMA_ATTR_USEBURST |

UDMA_ATTR_HIGH_PRIORITY |

UDMA_ATTR_REQMASK);

uDMAChannelControlSet(UDMA_CHANNEL_ADC0 | UDMA_PRI_SELECT,

UDMA_SIZE_16 | UDMA_SRC_INC_NONE | UDMA_DST_INC_16 |

UDMA_ARB_1);

uDMAChannelControlSet(UDMA_CHANNEL_ADC0 | UDMA_ALT_SELECT,

UDMA_SIZE_16 | UDMA_SRC_INC_NONE | UDMA_DST_INC_16 |

UDMA_ARB_1);

uDMAChannelTransferSet(UDMA_CHANNEL_ADC0 | UDMA_PRI_SELECT,

UDMA_MODE_PINGPONG,

(void *)(ADC0_BASE + ADC_O_SSFIFO0),

g_ui8RxBufA, MEM_BUFFER_SIZE);

uDMAChannelTransferSet(UDMA_CHANNEL_ADC0 | UDMA_ALT_SELECT,

UDMA_MODE_PINGPONG,

(void *)(ADC0_BASE + ADC_O_SSFIFO0),

g_ui8RxBufB, MEM_BUFFER_SIZE);

uDMAChannelEnable(UDMA_CHANNEL_ADC0);

ADCIntEnableEx(ADC0_BASE, ADC_INT_DMA_SS0);

IntEnable(INT_ADC0SS0);

/**/

}

Sequence step configuration is interleaved with ADC_CTL_CH0 and ADC_CTL_CH1, I dont know why always this happens in the fourth DMAs transfer.

Does anyone know why this is happening??, it is related to DMA transfer configuration???

Thanks in advance!!!