Other Parts Discussed in Thread: DRV8350, CSD19535KCS

We are designing a 1 Kw BLDC motor drive using drv8350R for a three wheeler vehicle.

The layout and schematics were designed in two iterations and the 2nd iteration was designed based on the suggestions from the E2E forum and was also uploaded for verification.

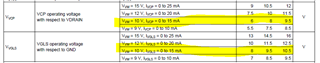

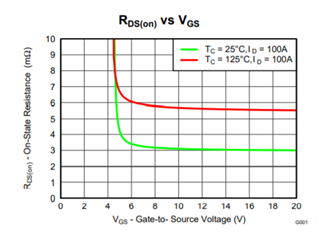

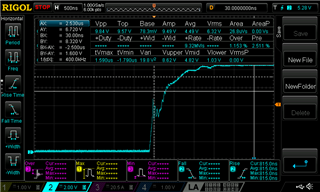

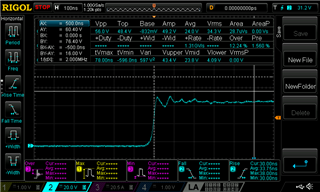

The boards were manufactured and the boards were operating perfectly. We loaded the boards upto 1.7 Kw on a dynamometer. Initially we faced issues with false triggering of Vds OCP, and we kind of solved it by increasing the drive current but to make it work the vds ocp level was set at least 6 times more than the theoretical calculated values.

After that when we started testing the boards on the actual vehicle, the vds ocp would still get triggered even with maximum deglitch time settings and increased drive current. The same boards are working on dynamometer, but not on the actual vehicle.

The Vds OCP is false triggering much earlier on the vehicle, even if the ocp levels are set at very high values.

The mosfet which we are using has 13nC Qgd and 3.1 mOhm RdsOn.

Gate drive current is set at 400/800 mA.

I know voltage waveforms are required for this but it's difficult to take waveforms on a moving vehicle.

I have attached the layout and the schematic for the inverter circuit.

Refer this for layout: 7455.Power_Board_V2.pdf

Refer This for schematic only:VCU_MCU_V2.pdf