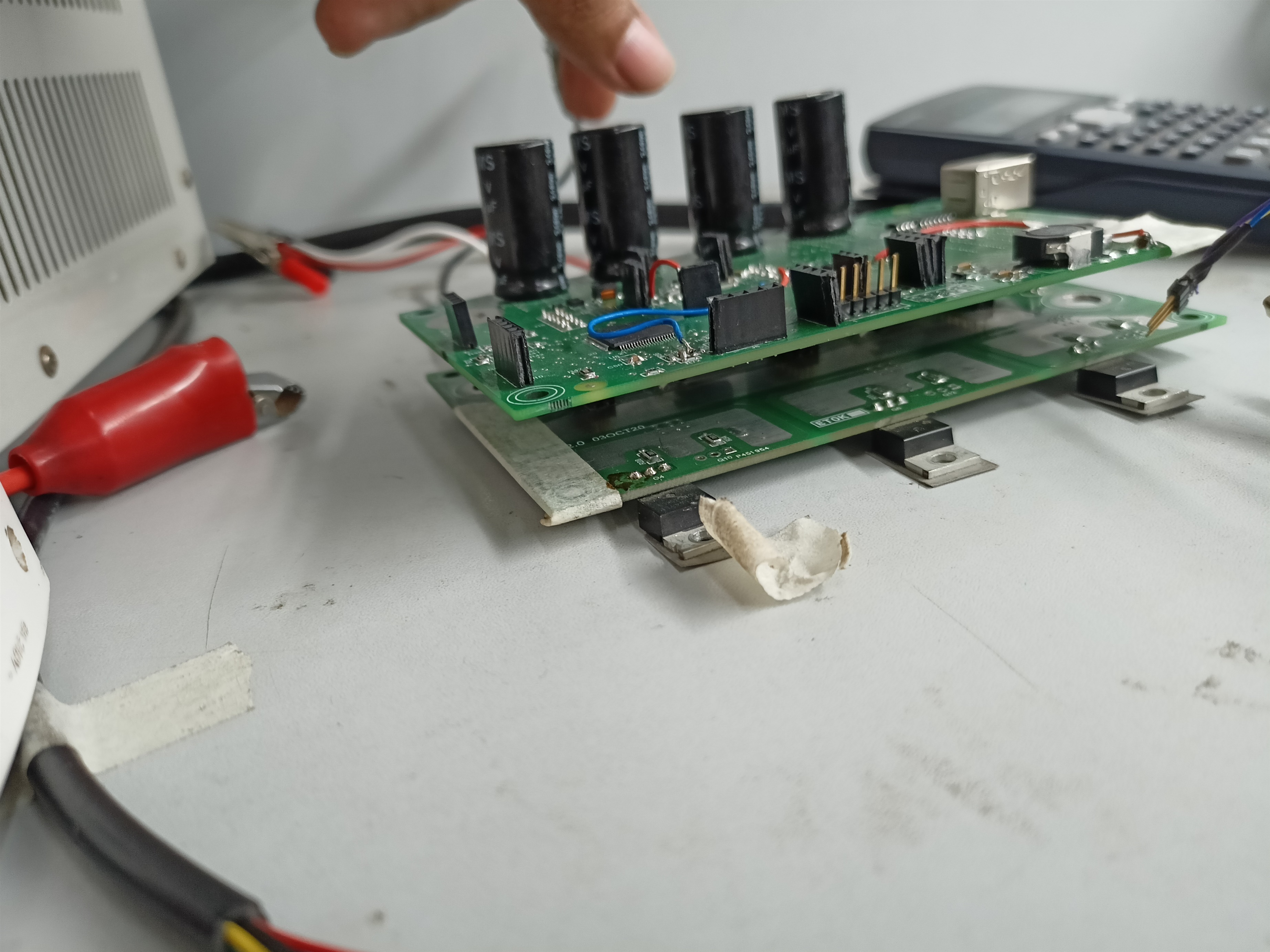

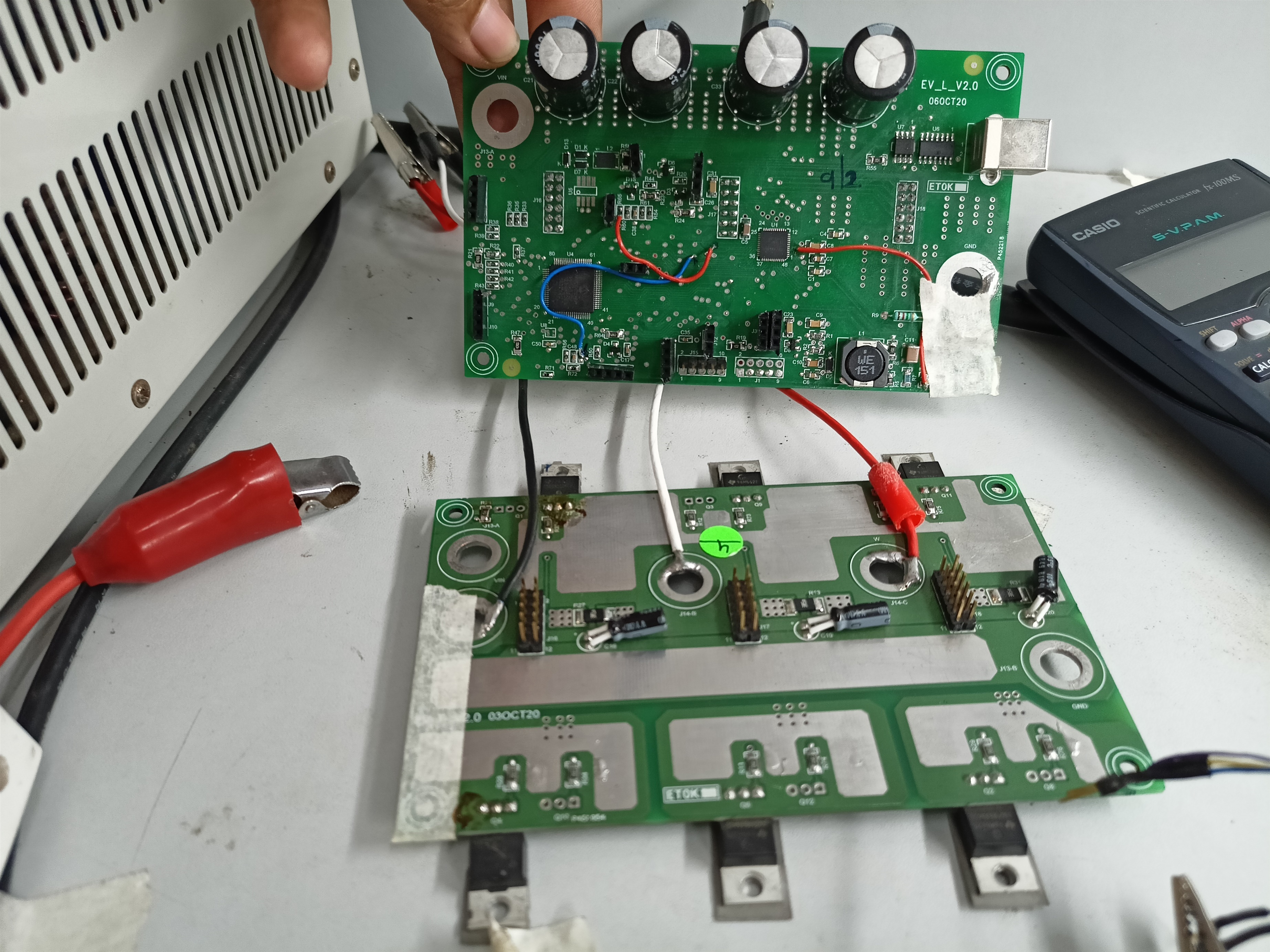

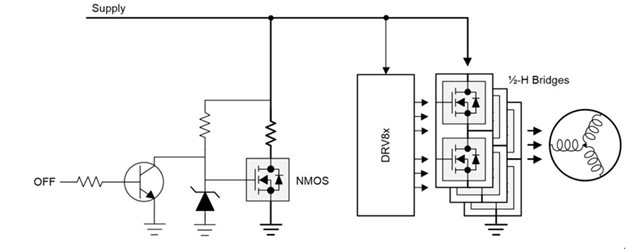

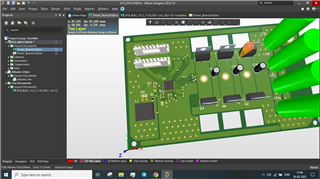

We are developing a motor controller unit using a DRV835RS5 Gate driver and DSPIC33ch Microcontroller.

The PWM frequency is set at 10KHZ and controller clock is set at 8 MHz.

The 8 pole BLDC motor has a rated RPM of 3200 at no Load 48 V.

I am implementing the commutation using a Timer Interrupt which is called every 5uS.

At higher RPM (>80% DC) the motor starts missing commutation and the gate driver stops the motoring.

The same application if implemented using polling, is working upto 85 % Duty Cycle., but I need to add extra functions in the MCU so I have to proceed with interrupts.

Can you help rectify the problem.