Other Parts Discussed in Thread: TPS54360B

Hi,

We are testing our custom hardware that used the DRV8353RS controlled by an STM32.

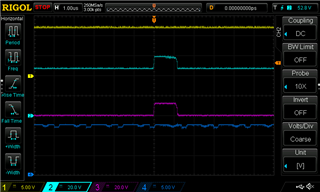

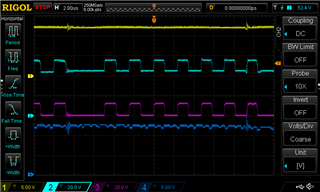

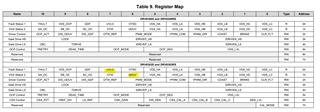

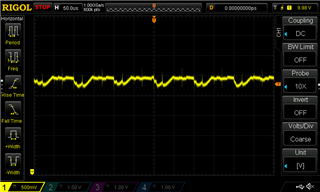

The main fault that we are getting is UVLO and GDUV, these occur at the same time.

The conditions for this happening seem to be high speed and about 20-30A load.

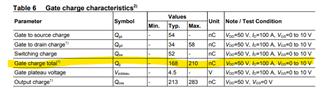

We are using fets with a Qgd of 34nC and an IDRIVE of 350mA. This ha been tested significantly on o controlled rig and the waveforms seem to be good, with almost no ringing at 15A (the maximum load we could apply) and temperature increase was acceptable.

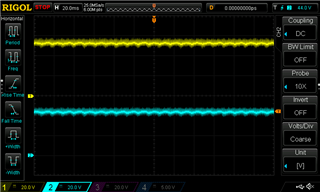

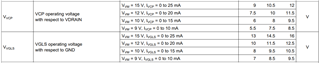

It seems strange that we would be seeing these two faults as we are using a 48V battery (testing has been done between 42 and 48V) and VM is 12V supplied by a TPS54360B (so should supply 12V down to at least 20V).

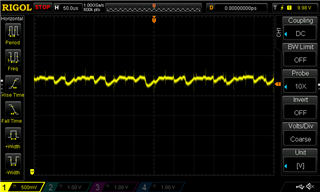

We have significant bulk capacitance (2 x 330uF), and capacitance on the 12V line (47uF electrolytic , plus 10uf and 100nF close to the DRV) so I would expect that a large voltage drop is not likely

Is there anything that we could try to eliminate this fault from occurring?