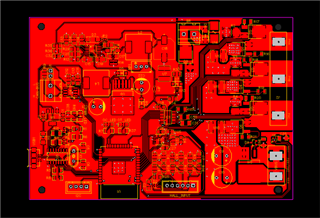

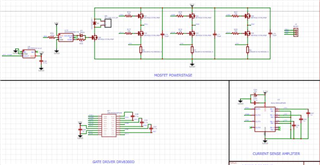

i am building a 3 phase BLDC controller for a 350Watt hub motor.

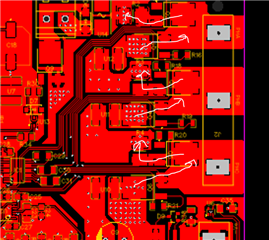

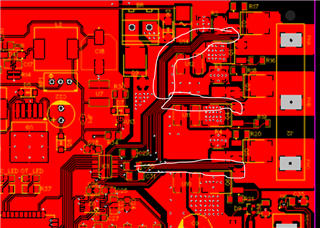

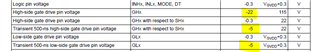

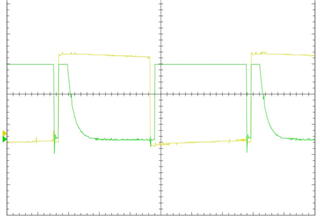

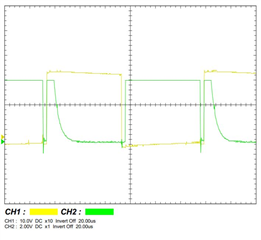

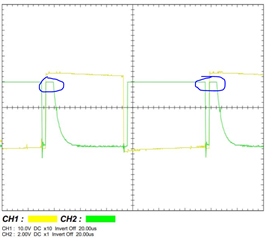

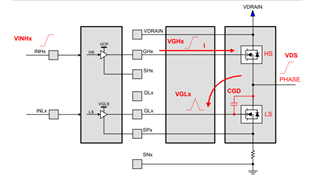

It is working fine so far but at higher target voltage (higher speeds) the mosfet are heating and there is a significant noise from switching. I am using 0.05% software deadtime but the highside mosfet seems to be not turning off immediately and is crossing the deadtime during turn off.

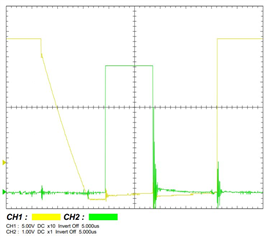

The graph below is between input signal to drv8300 ( Green waveform ) and high side output of drv8300 to mosfet ( yellow waveform ).

this issue with high side is there for all three phases. low side mosfet gate signal is perfect.

This condition is irrespective of load.

kindly support me with this.

Thanks you,

Syed Sameeullah,

CTO @ Enarxi Innovations Pvt. Ltd.