Hello,

When reading a value from a status register on DRV8343-Q1's SPI, which timing does a valid data come from the SDO?

Best regards,

Shinichi Yokota

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

When reading a value from a status register on DRV8343-Q1's SPI, which timing does a valid data come from the SDO?

Best regards,

Shinichi Yokota

Hi Yokota-san,

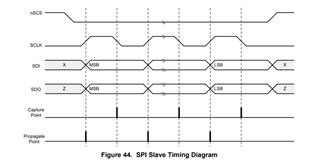

SDO data is propagated on SCLK rising edges and should be captured on SCLK falling edges.

Ensure SPI clock phase and clock polarity is 0 to read SDO outputs correctly. If you have questions please follow this E2E FAQ on SPI configuration and use: e2e.ti.com/.../faq-spi-configuration-and-use

Thanks,

Aaron

Aaron-san,

I've created a picture to explain the question. Is it correct?

Best regards,

Shinichi Yokota

Hi Yokota-san

Yes this info is correct. Please reference section 8.5 Programming in the datasheet.

Thanks,

Aaron