Hello,

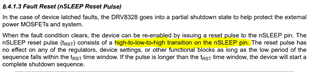

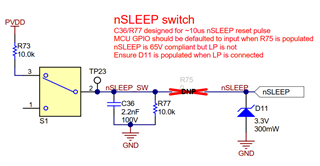

I have a question regarding the nSLEEP pin of the DRV8328 gate driver. From my understanding this pin can be used to put the device in sleep mode and to reset fault conditions without entering sleep mode when a low pulse is provided. I've actually found an evaluation board (see DRV8328AEVM) where this device is used. The snapshot below shows the circuitry for the nSLEEP pin in the evaluation board. nSLEEP goes straight into the MCU GPIO however it's not clear to me what happens if R75 is populated. It looks like switch S1 can be used to generate the pulse, however it's not clear to me if nSLEEP should still be connected to the GPIO of the MCU or not.

thanks

Giorgio