Other Parts Discussed in Thread: DRV8305

Hello,

I'm using the DRV8305NQ within a 24V / 350W BLDC motor electronics prototype.

The motor control is based on F280049 and instaspin FOC software.

The implementation is close to the DRV8305 evaluation board.

Basically the system is working as intended, but there is an issue concerning the quality of incoming phase current signals.

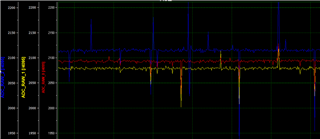

Monitoring the phase current signals by application software shows, that there are short disturbances with amplitudes up to 2A,

even if the powerstage is not switching. According instaspin FOC software, the signals are sampled in the middle of the lowside-FET ON-time,

i.e. there are no switching events in a certain time-span around the sample point. All three motor-phase-current-signals are sampled simultaneously,

each by one of the three ADC units of the F280049 controller.

The disturbance effects mostly all three signals at the same time.

The impact on signal Ia is least, on signal Ic most.

The amplitudes of the disturbances are rising by increasing the PVDD supply voltage (e.g. from 10V.....32V).

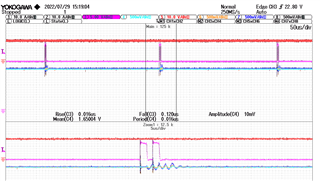

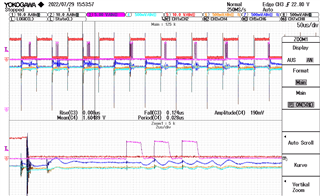

I could find a correlation between the disturbances and the operation of the chargepump of the DRV8305.

Pink: voltage at chargepump 'flying' capacitor CP2H

Blue: phase current signal

Red: phase voltage (const., no switching)

system without motor operation (no switching):

system with motor in operation:

The chargepump pulses (i.e. disturbances) are asynchron to the motor PWM switching and are drifting again and again into the ADC sample point.

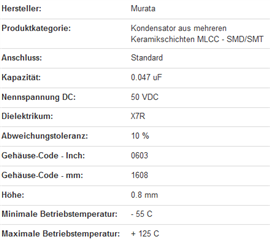

As background information : the phase current signal configuration is:

2mOhms shunt in the 'foot' of the half-bridge

amplification (DRV8305 amplifier) x20, (with offset 1,65V, i.e. 0A = 1,65V)

resulting in 40mV/A

On basis of 3,3V signal range, the theoretical current range is +/-41,25A

Using a 12bit AD-converter, the resolution is about 20mA/lsb

Is the obeyed effect basically known ?

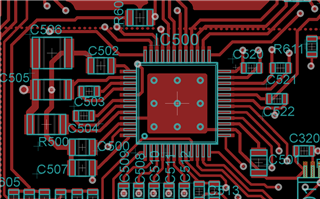

Up to now, I couldn't detect the effect on DRV8305 EVM. I suppose, this is due optimized layout.

The layout of our prototype hardware is mostly close to the EVM, but maybe not optimal.

Is there a possibilty to check some aspects of our design ?

How can I weaken the effect of chargepump influencing the measurement ?

note#1 : as a trial, I add a 12 Ohm series resistor in the current path of each flying 47nF capacitor, what effects a significant lower disturbance.

However, this is not acc. application note/ not intended for final design.

note#2: connecting the scope-probe (or a short piece of wire) on CPH2 had an effect on disturbance amplitude !

Friendly Regards

Martin Bayer