hi chip,

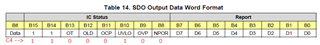

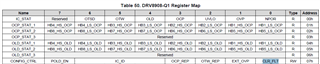

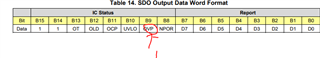

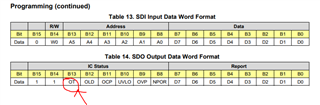

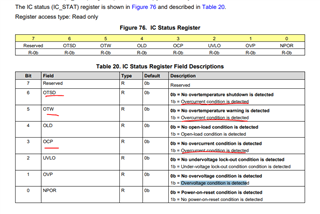

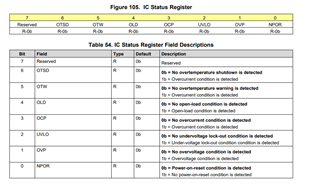

could you tell me why the first byte(0xc6 or 0xc4 or 0xc0) is not the same as the second byte0x04,when I try to read the IC status register?my question based on link (+) DRV8908-Q1EVM: SPI Messaging Details - Motor drivers forum - Motor drivers - TI E2E support forums

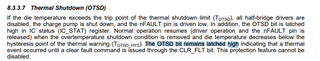

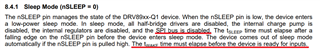

and i have anothere question ,when i write a register ,but SDO return a fault ,how to clear the fault in the register(when the hardware board dispper the fault )?