Hi TI Forum,

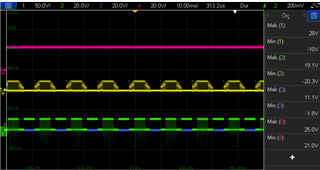

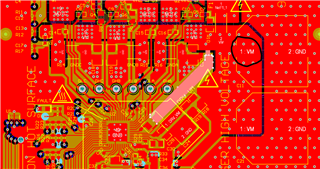

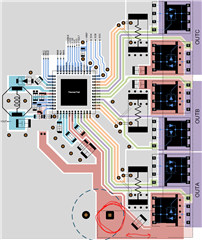

We are using DRV8353 smart gate driver. We have a trouble HS and LS mosfet switching and optimization of idrive, tdead, tdrive and gate resistor.

Our used mosfet has 100ns rise and fall time with 45nC gate-to-drain charge and 150nC total gate charge, typically.

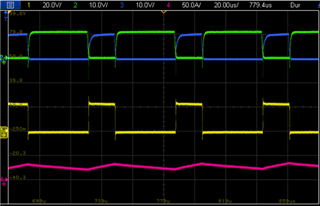

When we go with 22ohm gate resistor, there is less overshoot, undershoot and oscillation for gate and phase signals but more important HS and LS switching not correct.

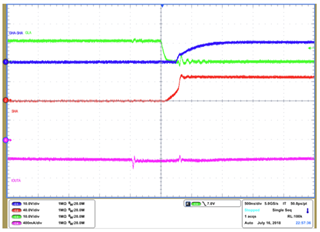

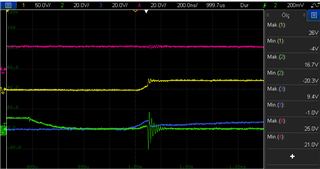

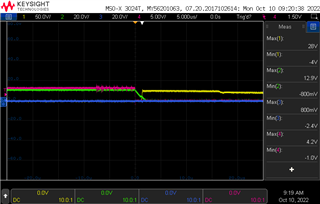

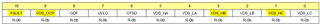

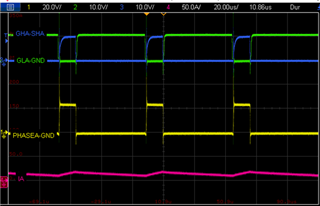

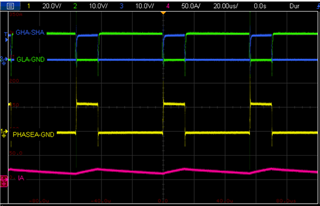

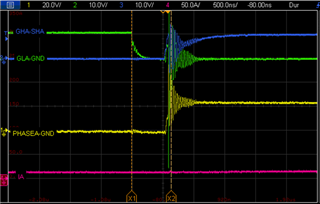

Blue=GHA-SHA Signal,Green=GLA-GND Signal, Yellow=SHA-GND Signal, Purple=Phase A Current

(Rgate=22ohm, I_drives=300/600mA, t_dead=400ns, t_drive=4000ns, 20A LOADED)

There is no affect increasing i drives for rising and falling time because of gate resistor limiting current.

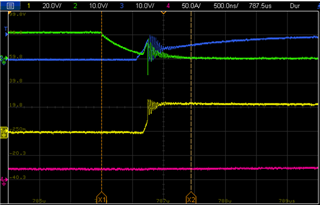

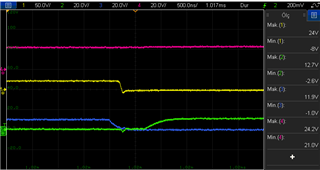

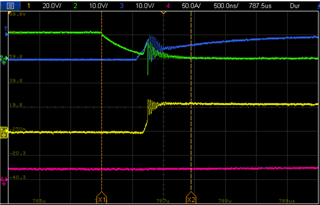

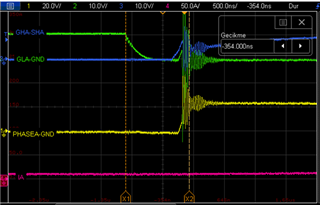

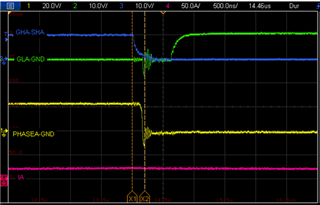

Other, if we decrease the gate resistor value to 2.7ohm, switching is correct but oscillation and other unwanted things happen at some time of switching.

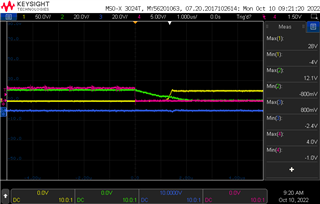

(R_gate=2.7ohm, I_drive=300/600mA, t_dead=400ns, t_drive=4000 ns, 20A LOADED)

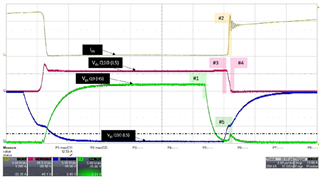

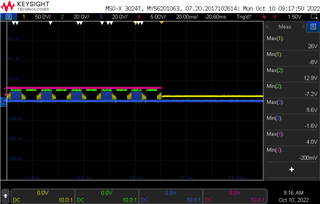

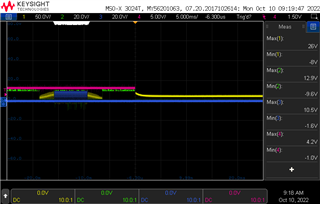

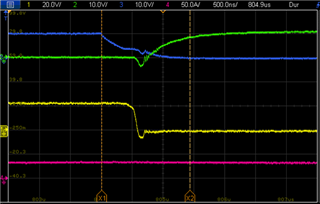

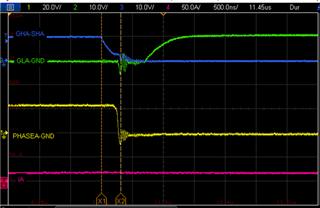

If we increase i_drive value, rising and falling times changes, but unwanted oscillations continue.

(R_gate=2.7ohm, I_drive=1000/2000mA, t_dead=400ns, t_drive=4000ns, 20A LOADED)

- Switching loss in 22ohm state is more than 2.7ohm one. So, thermal dissipation is so much on mosfets. We should decrease it.

- If we suddenly changed the load from 20A to 5A gate fault, overcurrent error happens in 2.7ohm gate resistor state. But, there is no error when we use 22ohm gate resistor.

- To decrease phase voltage overshoots and others, we have done suggestions on TI App Note System Design Considerations for High-Power Motor Driver Applications. The oscillations may be occur because of tdrive and dead time.

Can you help us in this issue? How can we overcome with this signal aliasing?

Thanks in advance.