Hi Expert,

I have some test on DRV8718-Q1 EVM and find some questions. PVDD is connected to 8V.

1. When stop gate drivers, I can still test 8V on all output pins. Take below HB1 as example, GH1=OUT1 =8V, GL=0. Is that normal?

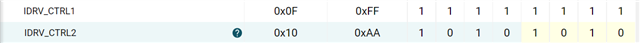

2. I change source & sink current capability. HB1has four times larger than HB2. But on the oscillators, the measurement is as below. It makes sense to the rising time difference, as 4 times. But for the falling time, why is only about 2 times larger whereas sink current capability is 4 times larger? May you help explain? Thanks.

| rising time | falling time | |

| HB1 | 72.66ns | 73.06ns |

| HB2 | 267.5ns | 174.3ns |

BR,

Elec Cheng