Other Parts Discussed in Thread: DRV8323

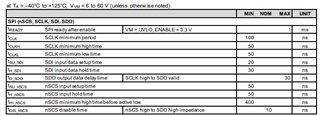

Clock frequency of sys_clk: 50 MHz;

Clock frequency of SPI_sck: 50 MHz/12.

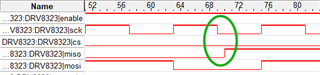

As shown in the figure, after CS is pulled low, I first configure the Gate Drive HS and Gate Drive LS registers:

Gate_Drive_HS = 16'b0_0011_011_1100_1000

Gate_Drive_LS = 16'b0_0100_111_1110_1110

Then read the values of Gate Drive HS and Gate Drive LS registers:

Gate_Drive_HS_RD = 16'b1_0011_000_0000_0000

Gate_Drive_LS_RD = 16'b1_0100_000_0000_0000

However, the SDO output signal of the DRV8323 chip is a bit delayed than my input signal, which causes the data I collect on the falling edge of SPI_SCK to be wrong.

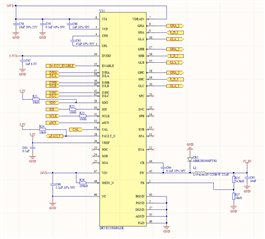

The peripheral circuit diagram of DRV8323RS is shown in the figure below.