As you mentioned we had connected SP, SN pin to GND, so there is no voltage gap between them now

but we face below situation.

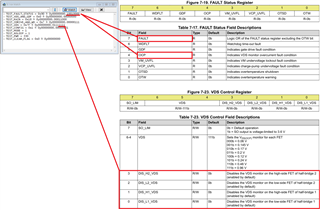

All VDS monitor function is disabled and SP-SN voltage difference is '0' but OCP flag is HIGH when we input 33[%] PWM duty cycle in IN2 pin

(MODE is '1', IN1 is HIGH, under 32[%] duty cycle is fine, PWM frequency is 80[khz])

Can you tell me any possibility about this problem?