Other Parts Discussed in Thread: MCF8329A

Hi All,

I have a custom board design that I have been working on and have run into OCP_VDS and OCP_SNS faults frequently.

This issue seems to be random from board-to-board. That is, of the prototypes I have tested, some immediately work, and some immediately fall into a fault condition. Each board gets loaded with the same known 'good' registers before attempting to run.

For the boards that fall victim to the fault, I have found that more often than not when a fault occurs the commutation FETs become damaged in high-side/low-side pairs, which led to the suspicion of cross-conduction. I have been able to gather a lot of evidence to support this, and as a result have improved signal integrity and immunity, but have thus been unable to determine the root cause, and so, the problem persists.

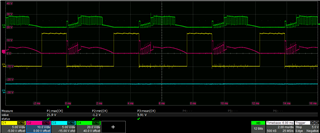

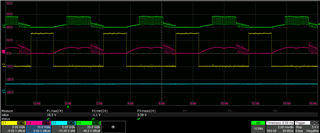

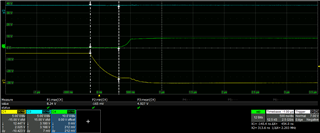

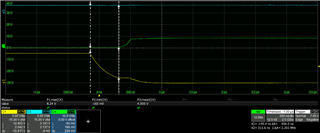

The following scope shots show the high-side and low-side gate drive signals during Startup alignment for a known good (able to run) board and a faulty board that immediately triggers an OCP_VDS fault: Each board is identical in hardware and software.

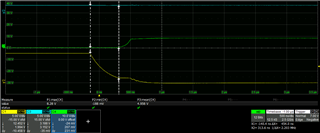

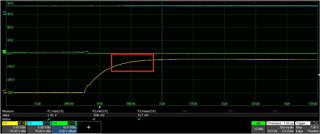

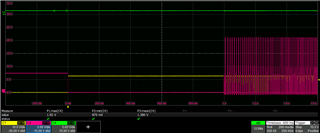

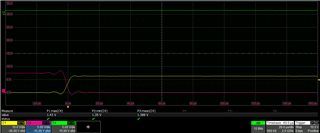

Good Board - Macro scale and zoomed in. Red = high side; Yellow = low side; Green = CSA_OUT; Input Voltage = 9V:

In this case, the board starts and runs at it should. The high-side gate is being pulled Low as the low-side gate is pulled High. Even though the board runs, I still suspect some amount of cross-conduction as both gate voltages converge slightly above the gate threshold voltage. If I increase the input voltage to >22V, a OCP_SNS condition is to be expected as each gate voltage will be slightly higher. If, in this case, cross-conduction is occurring, then it is not enough to trigger a fault condition, and may or may not be true up to ~22V.

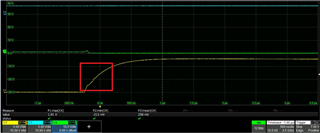

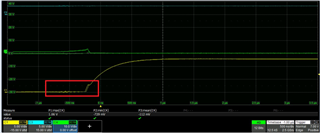

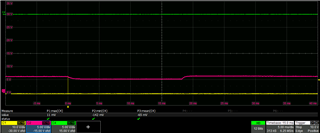

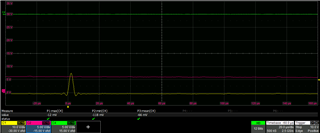

Faulty Board - Macro scale and zoomed in. Red = high side; Yellow = low side; Green = CSA_OUT; Input Voltage = 9V:

The above scope shots were taken during startup on one of the faulty boards. As we can see, as the low-side gate gets pulled high during initial alignment, the high-side gate fails to get pulled low. In this condition, it is suspected that both high-side and low-side FETs are effectively conducting leading to a cross-conduction condition. This would explain the OCP_VDS fault trigger. I also suspect that if I increase the input voltage that I will trigger either an OCP_VDS fault or an OCP_SNS fault and likely damage the FETs - this has been the case on other boards. The reason to start with a low (9V) input voltage was to hopefully prevent damage to the FETs while attempting to solve the issue (thus far, it does not seem as if my FETs have been damaged, but the fault persists).

My investigation into this issue has been extensive both in terms of hardware and in software. I have tested for undesired shorts and opens, and compared the measured point-to-point impedances and component values of the 'good' board to the 'faulty' board used in this data collection and have only found negligible variations due to tolerances.

I am here now in hopes that someone may be able to offer some insight into:

- What might be the cause of the High-side gate not being pulled low during startup

- What I might be able to check for (chances are good that I have already)

- The likeliness that this is a design/layout issue, and why it would be so random/unpredictable from board-to-board

- The likeliness that this an IC (MCT8329A) issue

- If it is common, and if there is a known fix

I understand you may not be able to answer all my questions, but I am running out of directions whilst chasing this problem. Any and all insight will be greatly appreciated.

Thank you for your considerations.