Hello All,

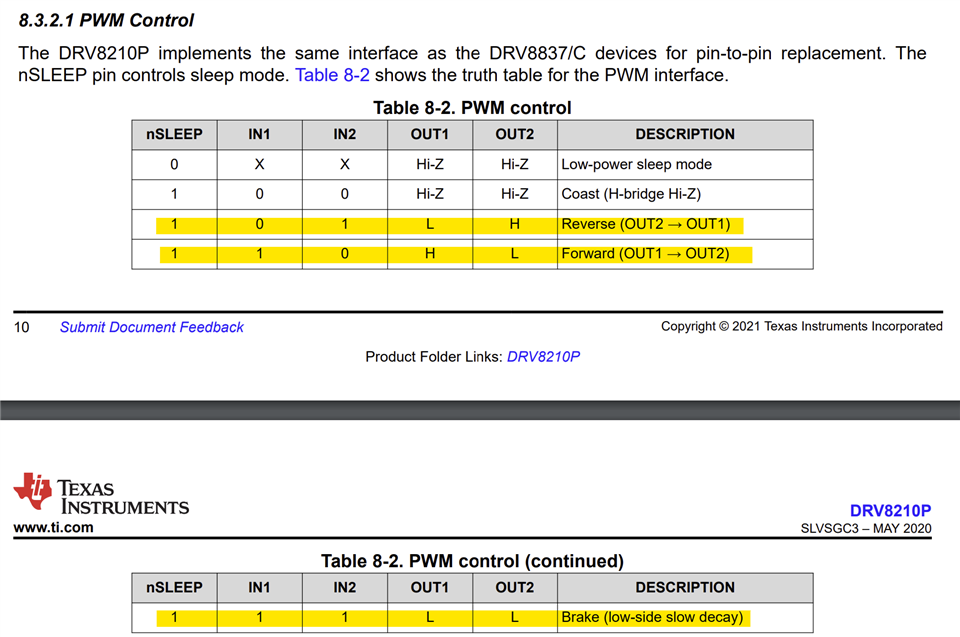

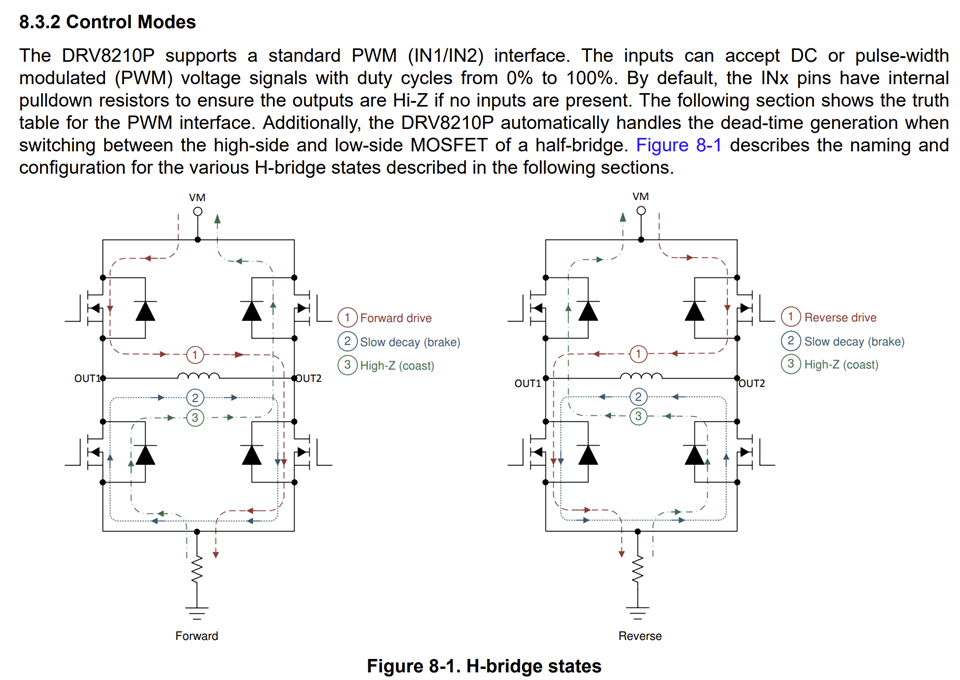

From the datasheet:

The DRV8210P datasheet (May 2020) section 8.1 mentions: "With separate motor (VM) and logic (VCC) supplies, the VM voltage can drop to 0 V without significant impact to R DSon and without triggering UVLO as long as the VCC supply is stable".

What happens when the VCC and VM is not split as I see there is a kick back happening when taking the H-bridge from ACTIVE mode to SLEEP mode. Any thoughts on this please?

I have this part on a single supply and there is a kickback reaching ~3.9V momentarily between ACTIVE to SLEEP mode which is not ideal.