Tool/software:

Hi TI Team,

We are currently working with the DRV2700 in our design and have encountered an issue during FEMA testing.

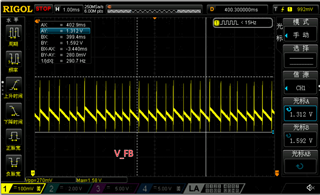

Under the conditions where the EN pin is enabled and a signal is provided to IN+, we intentionally shorted OUT+ to OUT– (and also tested with OUT+ shorted to GND). During this short circuit, the total system power consumption spiked to approximately 5 W (for reference, the standby power consumption with EN enabled is about 0.7 W).

After maintaining the short circuit for a few seconds and then removing it, we observed that the system power consumption did not return to normal levels—even after re-powering up the device. Additionally, we noticed that the input inductor (XFL4020-472MEB) reached temperatures exceeding 100°C. Upon removing and testing the inductor, we found its inductance had degraded to about 2 μH. After replacing the damaged inductor with a new one, simply enabling the chip (without any load) resulted in a power consumption of 2 W and the chip heating up to around 60°C. This suggests that both the DRV2700 and the inductor were damaged due to the short circuit on the output.

Our circuit configuration is as follows:

- REXT: 10 kΩ

- Rfb1: 806 kΩ

- Rfb2: 10.5 kΩ

We have a few questions regarding this issue:

-

Inductor Damage: Based on the power consumption during the short circuit, it seems the input current did not reach the inductor's saturation current nor the current limit set by REXT. Why did the inductor fail under these conditions?

-

Protection Mechanisms: Does the DRV2700's thermal shutdown feature not activate in this scenario? Are there any overcurrent protection mechanisms inherent to the chip that should prevent this kind of damage?

-

Output Signal Considerations: Our application requires a DC step output, potentially transitioning from 0 V to 100 V instantly. If overcurrent is a concern with such rapid voltage changes, would you recommend implementing a slew rate limitation to mitigate this issue?

Thank you for your assistance!

Kind regards,

Cain