Tool/software:

hi,

I have a question about IC_Status_Register Register:

Scenario:

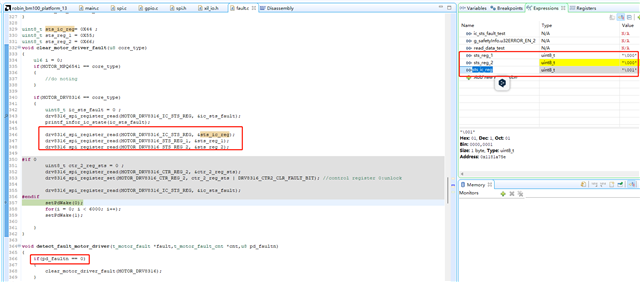

I don't have a motor hooked up, and after running for a while, the nFAULT IO is pulled low and the value of IC_Status_Register Register is read as 0X01, which means that only the Device Fault Bit is set.

Question

1. what is the definition of Device Fault Bit, I didn't find it in the datasheet ?

2. whether Device Fault Bit represents a total fault, but other sub-faults are not set?

Thanks