Other Parts Discussed in Thread: LAUNCHXL-F28379D, , LAUNCHXL-F28027F, , MOTORWARE, CONTROLSUITE

Tool/software:

Hi Team,

I am using DRV8305 booster pack with LAUNCHXL-F28379D board.

I have configured SPI A to communicate with the the booster pack via SPI.

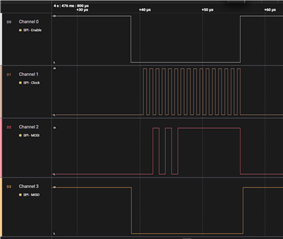

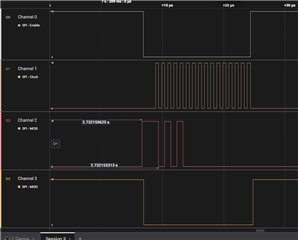

I am trying to write and read back the SPI registers to confirm whether SPI is working or not.

I observe that SPI write is not happening successfully. I am reading back the register after writing to it.

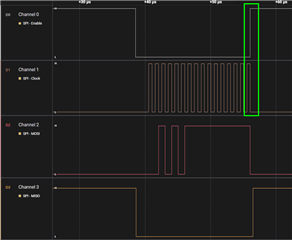

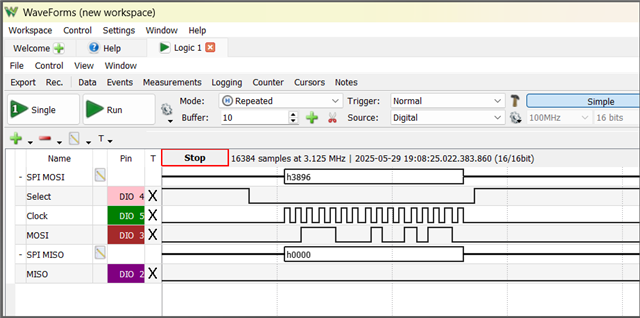

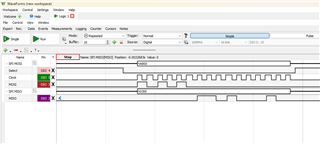

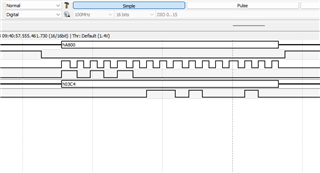

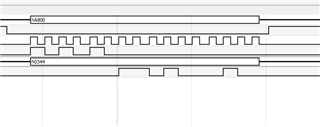

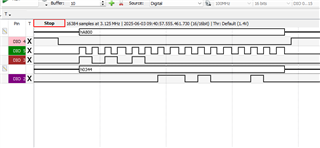

Bellow is the waveform of write command - 0x2BFF; /*0b00101 011 11111111*/;

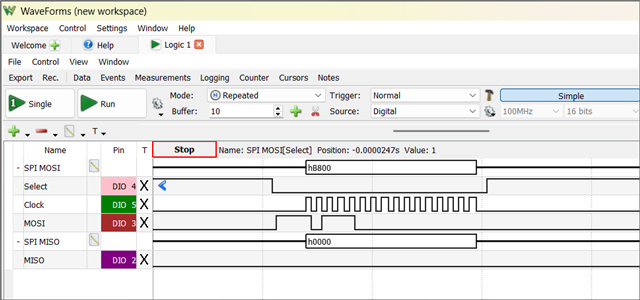

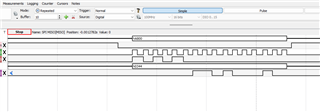

And below is the waveform of read command - 0xA800; /*0b10101 000 00000000*/;

_

I have provided 20 volts to the Booster pack and also set the EN_GATE pin

This is how my code looks like: