Hello

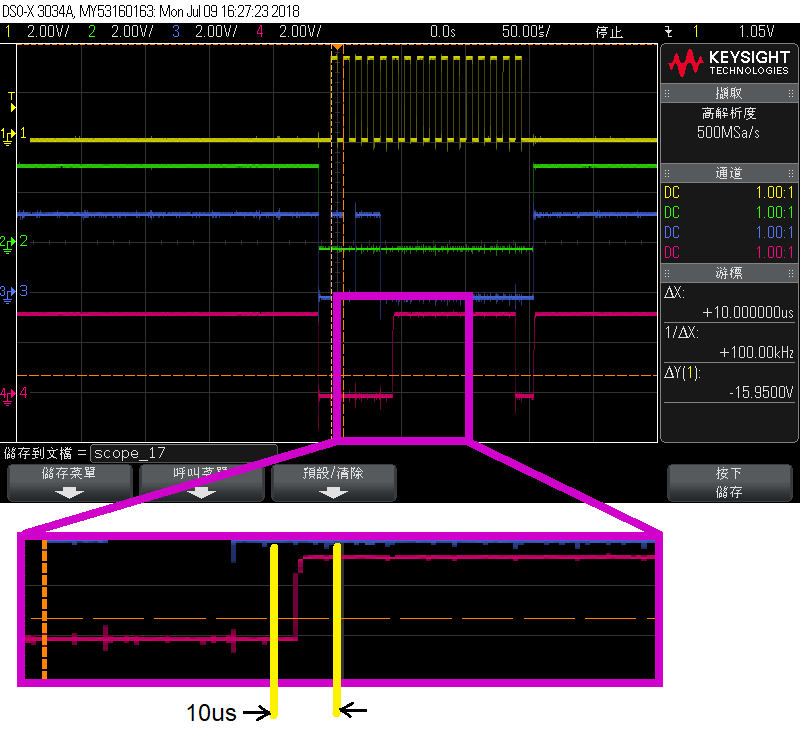

I have the same issue: the SDO singal is released by the DRV8323 too slowly. According datasheet max. 30ns, in our case about 600ns.

The SDO has an 4.7k Ohm pullup resistor to 3.3V. The 3.3V is stable, The SDO wire is about 4mm long on the PCB and nothing else is connected to it than the pullupresistor and a 6cm long wire wrap for the oscilloscope probe. I adon't think that the very little soldering flux on the PCB has an impact.

Any Idea why, the SDO is released so slowly?

Thank you and best regards

zoomed in: