Other Parts Discussed in Thread: DRV8350,

Hello dear TI Supporot team

I would like to use the IC in 4 quadrant (servo) operation. By using the INHA pin on high and the INHC pin as pwm Pin.

This works fine with 24V but I need to use 48V. Since the IC is designed for up to 60 V that shoud work I guess using VM=48V.

But it broke after a short time. Is there something you have to consider with VM= 48V? e.g. lower CVCP.

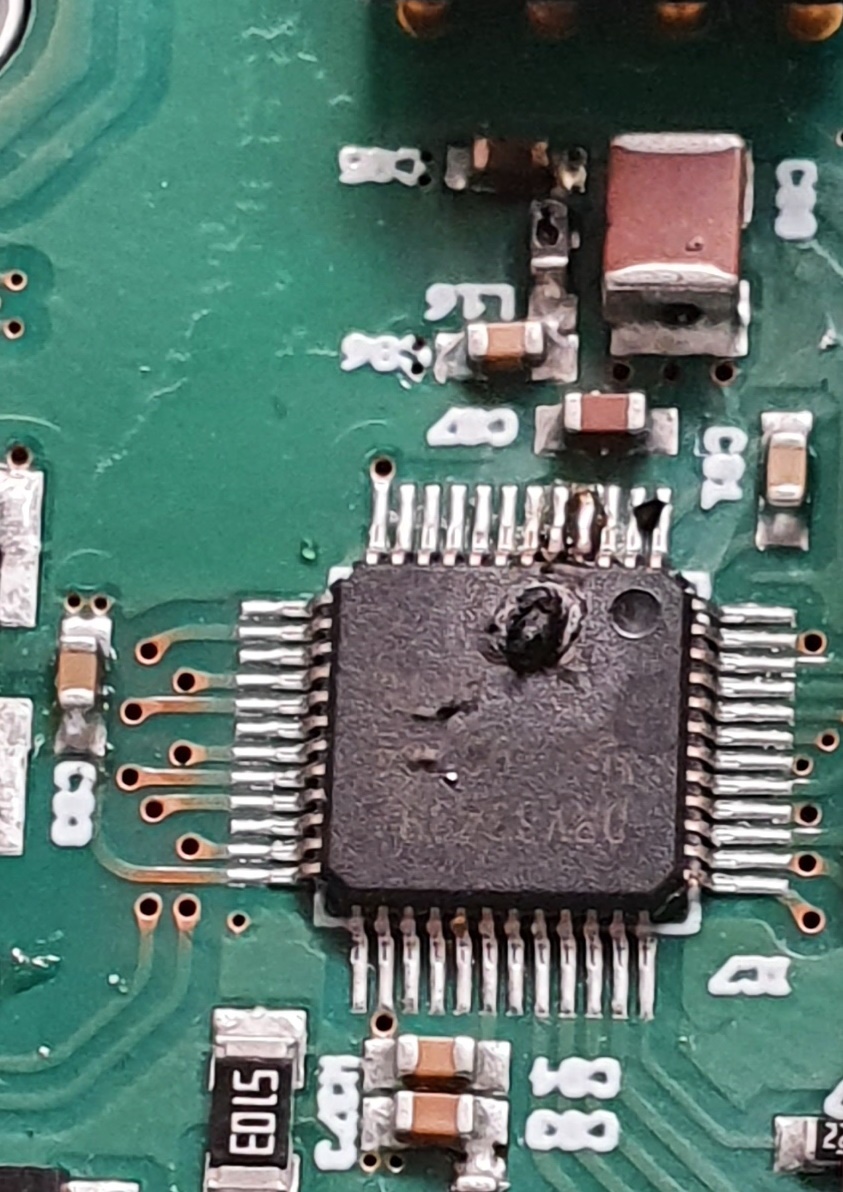

This is Picture of my circuit:

DRV8343H.pdf

Sincerely, Patrick Stubner.