Other Parts Discussed in Thread: DRV8320

Hi,

I built several motor controllers yet with the DRV8320R gate driver and until now i never had any problems.

In the current application, the input voltage may vary between +-5V and can change in several us (motor acts as a generator

and the chopper brakes it). On two controllers it destroyed me the gate driver and the low side MOSFET, possible because

of false error handling from my side (reset the DRV8320 after an error occured). The thing is, that there occur sometimes gate

errors (GDF), which need a manual reset of the driver and I don't understand yet, why this gate errors occur. It comes up when the motor

acts as a generator with around 20A, the voltage still seems stable through the current chopper.

So, what can I possibly do to prevent this GDF? Is it possible, that the charge pumpe comes to its limits and to reduce the maximum gate current may be a solution?

Further, should I add additional buffering to the gate driver for example with a schottky diode followed by a 100uF cap?

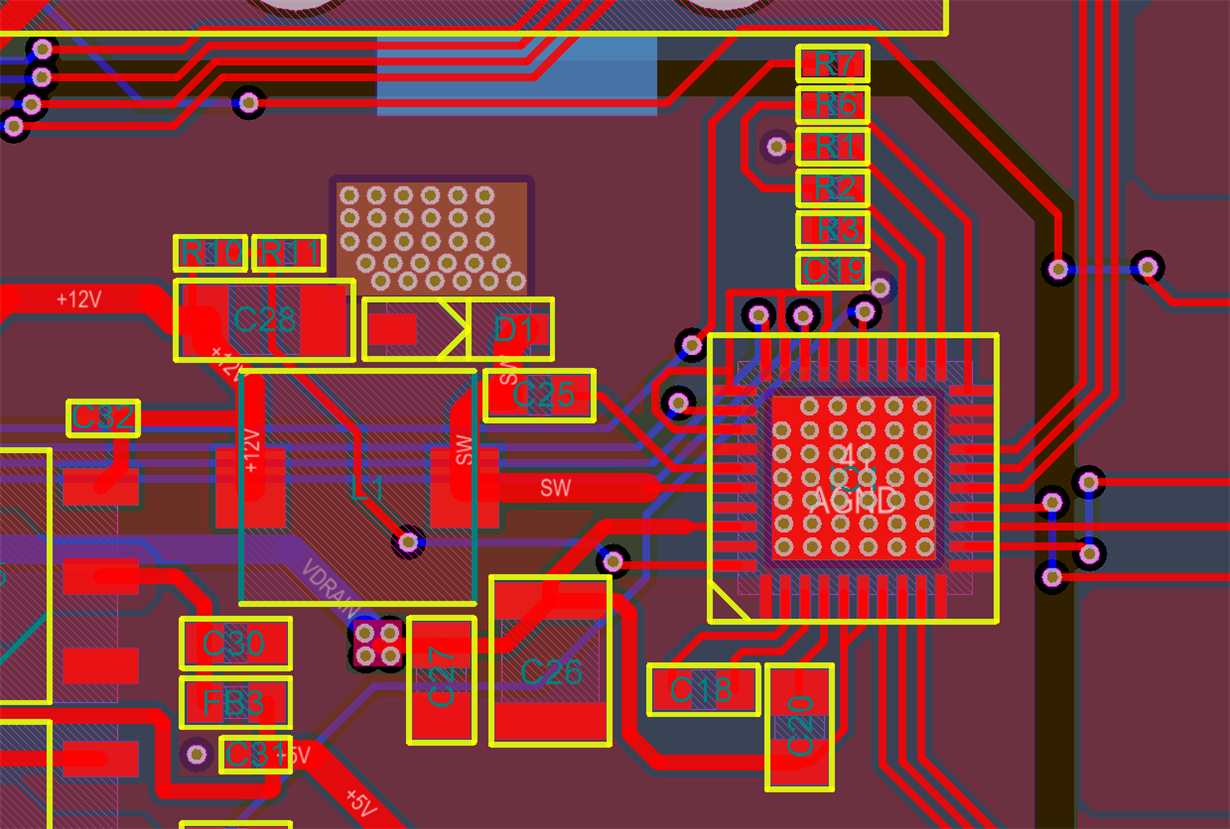

From the layout side, I spent a separate GND plane to prevent some latchup through high current. There is also a lot of buffering of the

VDRAIN supply. So far, I never had any problems of instability with this kind of design.

- 20kHz PWM frequency

- 1/2A gate drive current

- 2xBSC019N06NSATMA1 MOSFETs (around 102nC gate charge) --> Are two MOSFETs in parallel a problem for the driver?

- 48V input voltage