Hello, technical support

About drv8860 fault register read timing problem consultation.

1. The beginning and end of the timing sequence in MSP430 reference routine are different from those in the data manual. For example, the last latch should be low level, and the statement of routine is commented.

2. Read the fault register data in strict accordance with the time sequence of the data manual, and found that the highest and lowest bit of data are incorrect, so refer to MSP430 routine to modify the program.

3. Now it is found that the first reading of fault register data is correct. Once the reset fault register operation is executed, the data read immediately after fault register reading is wrong, which is similar to moving one bit to the left, that is, the highest bit and the lowest bit error. So I added "CLK" to the beginning of the sequence_ H”“CLK_ In this way, it is correct and correct, but we can't find the basis and I don't know whether it is feasible.

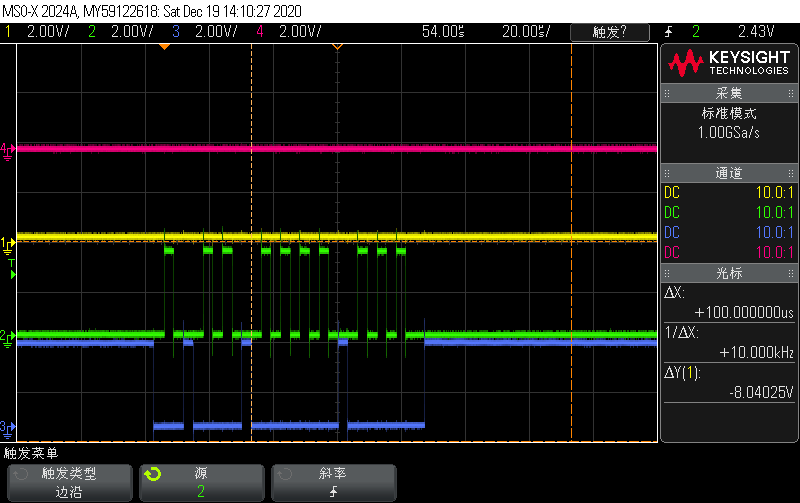

4. The figure below is the test waveform according to the routine. All 8 out are open circuit, the data read theoretically should be 0x00ff, and the measured data is correct for the first time. After the fault register is reset, the data read again is 0x01de

5. The figure below shows the test waveform of adding an extra clock pulse before reading the fault register timing according to the routine. All 8 out are open circuit. The data read in theory should be 0x00ff. The measured data is correct for the first time. After resetting the fault register, read the data 0x00ff again, which is still correct. Continue to try to restore the normal connection of different out interfaces and open circuit and short circuit test, and the reading is correct.

Blue is dout, green is latch, and yellow is CLK

The following is the procedure of this part, please see if it is feasible.

uint16 DRV8860_ReadFault()

{

uint16 dat=0;

uint8 i;

CLK_H();//

CLK_L();//

CLK_H();

LATCH_H();

CLK_L();

LATCH_L();

CLK_H();

LATCH_H();

for (i = 0; i < 8; i++)

{

CLK_H();

CLK_L();

dat <<= 1;

if (DOUT_PIN) dat |= 1;

}

for (i = 0; i < 8; i++)

{

CLK_H();

CLK_L();

dat <<= 1;

if (DOUT_PIN) dat |= 1;

}

DRV8860_Delay();

//LATCH_L();

return dat;

}

while(1)

{

drv8860.stu_fault = DRV8860_ReadFault();

b_8860_Hot = (drv8860.stu_fault) ? 0 : 1;

if (!b_8860_Hot)

{

DRV8860_RESET_FAULT_CMD();

}

Delay_ms(10);

}