Hello Peter,

We have incorporated below list of changes in the design.

FB15= 330ohm ferrite bead (MPZ2012S331AT000)

C589= 820pF

C590= 22uF

C101=10nF

R789= 3R3

R790=10R

also added 0.1uF on parallel to C590 & C64

I have added 3R3 resistor between boot pin and C85(0.1uF)

Snubber value is the 5.1R and 150pF.

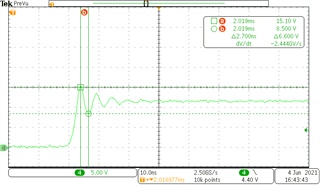

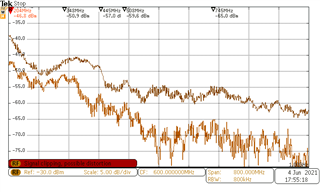

Here is the Switching & EMI result on in-house spectrum analyzer.

still we are getting the major ~200MHz peak.

Let us know how to remove this 200MHz peak.

Also other noise are improved respect to previous results but still its not good to go for final certification.

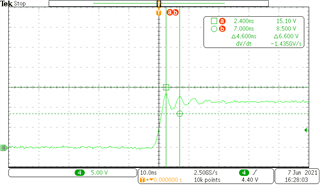

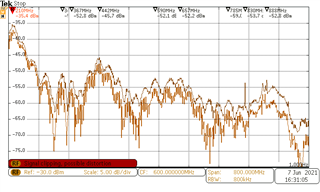

also i have changed the snubber value 2R2 & 2.2nF

Here is the results.

Let us know the snubber value range to test various combination.