Other Parts Discussed in Thread: SN6501

Hi expert,

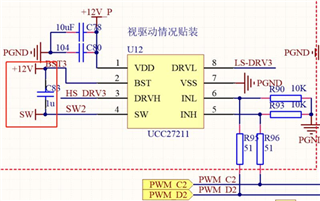

In customer's design, Vin of buck is 80V, Vout is 60V. However, there's 30V pre-bias on Vout when start up. This bias cause the the VHB to VHS differential voltage is below the specified threshold, and UCC27211 enters UVLO. Do you have any suggestions to help start up with this bias for UCC27211?

Beside, customer has an idea, which is to add a 12V isolated float power supply between VHB and VHS. UCC27211 won't enter UVLO with this isolated power. Do you think is there any risk with this method? Thanks.

Regards,

Jiandong