Hi

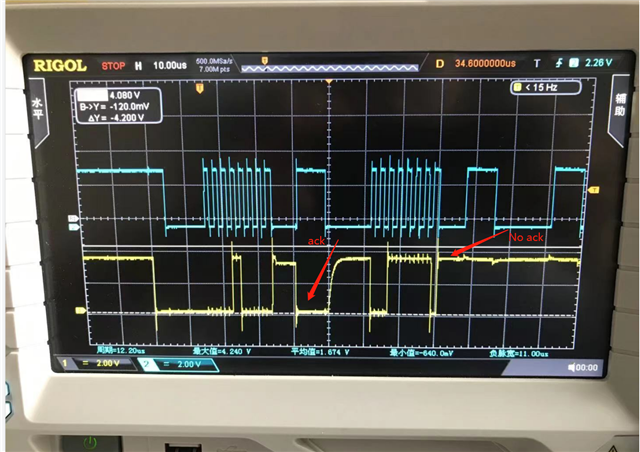

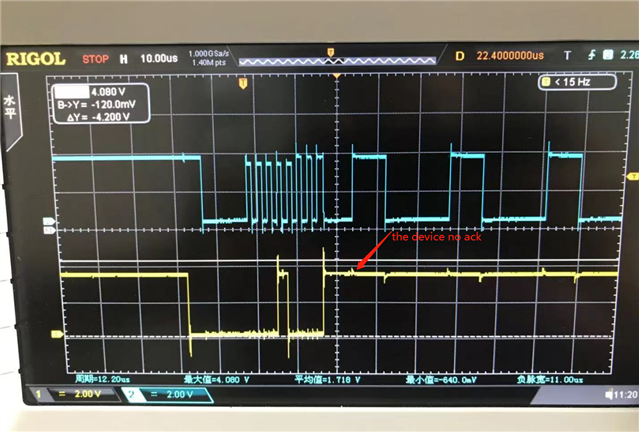

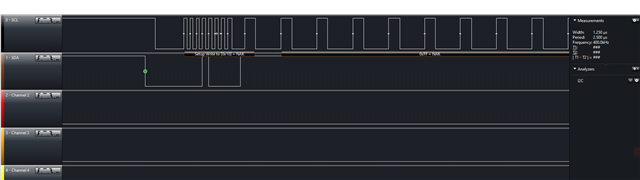

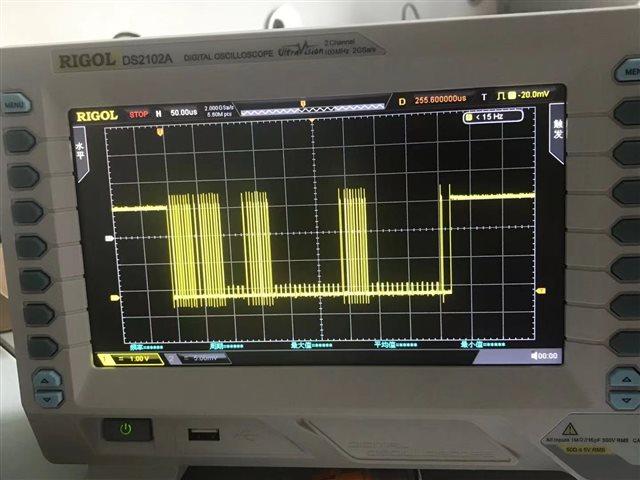

When driving bq76952, I found that the response of IIC is very unstable. After sending the device address 0x10, sometimes there is a response, sometimes there is no response, most of the time there is no response, and the communication is unsuccessful.

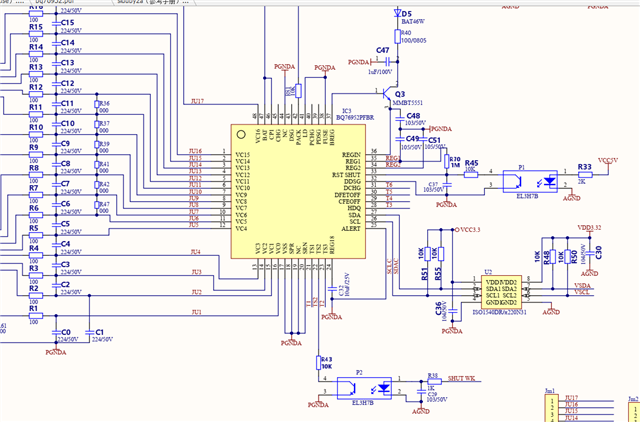

Attached the part of schematic

The cpu and the device are connected through the isolation chip, after the isolation chip is removed, directly connected, the phenomenon is the same.

please give some suggestions.

Thanks

Star