Hi,

I have a LM5116 controlled buck converter that is having a few issues during short circuit. It is used in a multi-output converter so is synchronized to an external clock via the RT pin.

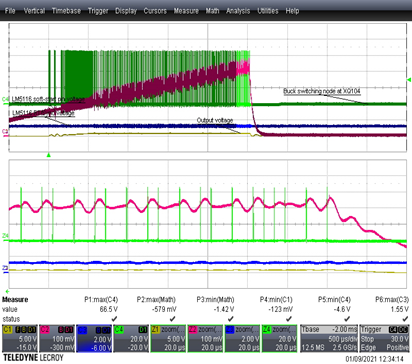

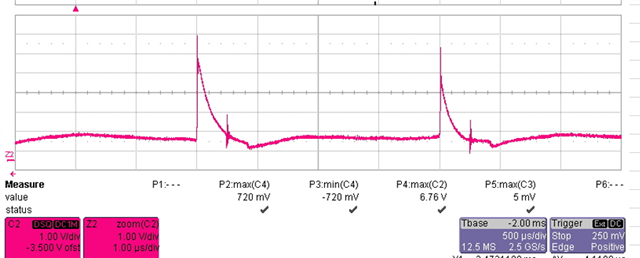

During overload or short circuit switching stops as expected after 256 cycles, then about 100µs later the High-side driver kicks back into life causing the output to rise again as shown below:

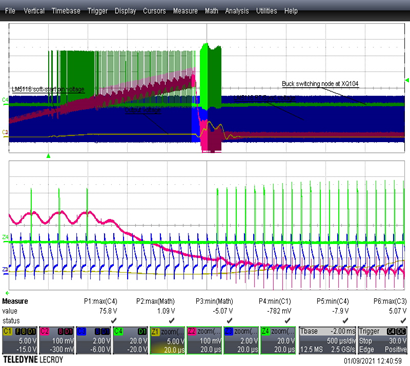

If the external clock is disconnected and the LM5116 allowed to free run the short circuit behaves as it should, initiating a proper hiccup cycle after 256 cycles. For reference I'm using a 10µF ceramic as my UVLO capacitor.

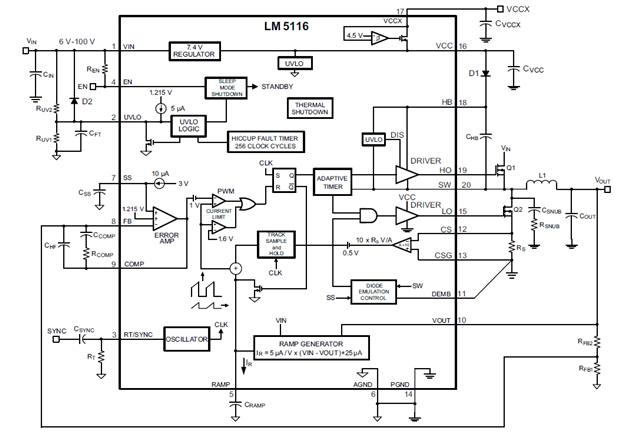

Looking at the block diagram I cannot see any obvious reason why the behavior would be different.

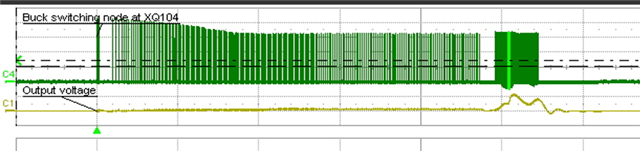

There is a little overdrive above the recommended 5V, but the sync signal appears to be within the limits allowed by the datasheet:

Any ideas as to what might be upsetting the chip?

(NB. Vout, HO, LO and SW are all clamped heavily at the chip's inputs to prevent negative over-voltages)

Quinn Kneller