Dear *,

we designed in LMR36520ADDA for three different voltage rails 3.3V , 9V, -9V.

Schematic for all three converters:

Efficiency measurements for all three converters:

1) 3.3V, please can you confirm that the scope graphs are as expected?

Vin = from 12V to 24V

Vout = 3.3V

Iout_max = 2A

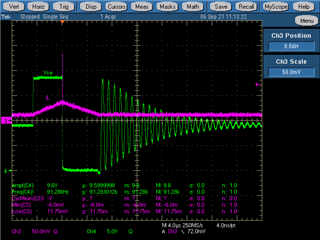

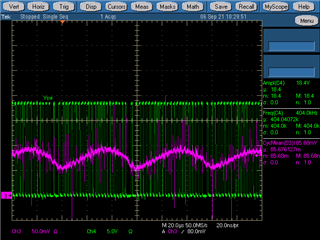

1a) no load switching point (PFM)

1b) 200mA load switching point (PFM boundary PWM)

1c) 400mA switching point (PWM)

--------------------------------------------------------------------------------------------

2) 9V, please can you confirm that the scope graphs are as expected?

Vin = from 12V to 24V

Vout = 9V

Iout_max = 1A

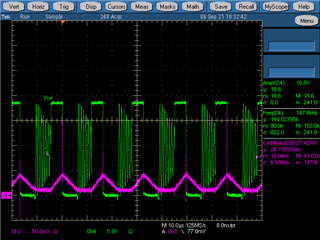

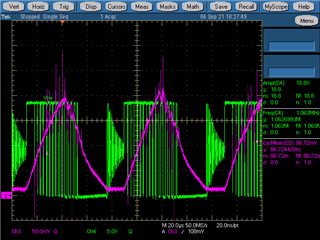

2a) no load switching point (PFM)

2b) 140mA load switching point (PFM boundary PWM)

2c) 400mA switching point (PWM)

--------------------------------------------------------------------------------------------

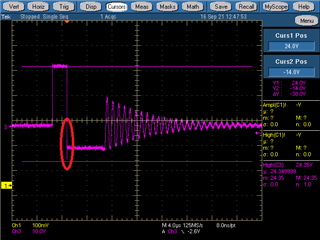

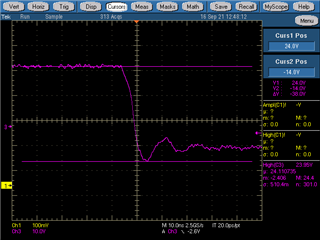

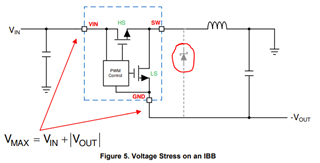

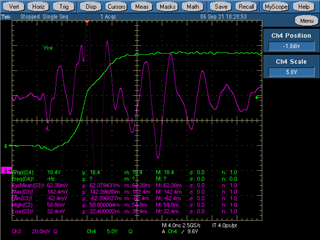

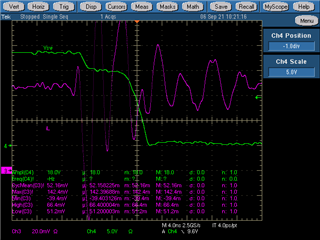

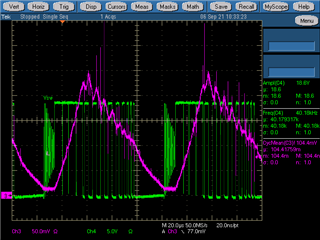

3) -9V, Here we have problems

3a) we hear audible noise when Vin is 12V and the load current exceeds 600mA

3b) we have negative spike when Vin is 24V

Vin = from 12V to 24V

Vout = -9V

Iout_max = 1A

3c) no load switching point Vin 12V (PFM)

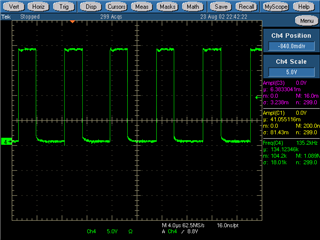

3d) no load switching point Vin 24V (PFM) -> negative spike

3e) 50mA load switching point Vin 12V (PFM)

3f) 40mA load switching point Vin 24V (PFM) -> negative spike

3g) 200mA load switching point Vin 12V (PWM)

3h) 400mA load switching point Vin 24V (PWM) -> negative spike

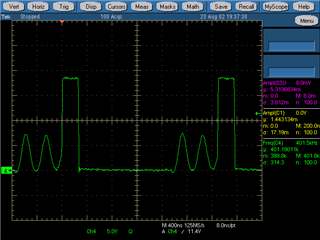

3i) 700mA load switching point Vin 12V -> audible noise

3j) 500mA load switching point Vin 12V -> transition to audible noise

--------------------------------------------------------------------------------------------

additional information for audible noise

@ Vin=12 V noise when exceeding 600mA

@ Vin=13 V noise when exceeding 630mA

@ Vin=14 V noise when exceeding 1000mA

--------------------------------------------------------------------------------------------

additional information for negative spiking

when exceeding Vin=19V we start to see negative spiking

--------------------------------------------------------------------------------------------

Best Regards,

David.

(Ch1 - V_out transient, Ch2 - Load Voltage transient)

(Ch1 - V_out transient, Ch2 - Load Voltage transient)