Other Parts Discussed in Thread: BOOSTXL-TPS650861, MSP430F5529

Hi,

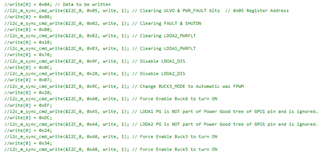

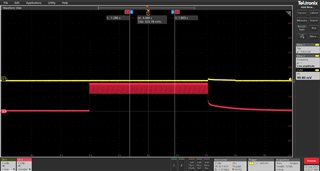

In continuation with my previous debugging query (Before I wanted to bypass BUCK 6 as per your previous recommendation. Also like Bypass means to cut open traces of BUCK6? If we leave BUCK6 unconnected still there will be a Power fault right as i saw in one of the link from IT [FAQ] TPS650864: What to do with unused voltage regulators / rails? - Power management forum - Power management - TI E2E support forums), I wanted to find out and confirm where exactly the Power fault occurred and hence trying to connect I2C BUS to access Power Fault status registers, but i am seeing that the I2C lines on the PMIC are not up and in Idle state the voltage reads as 0.7V to 0.8V. The pull-up resistor is 2.61K ohms and we are trying to connect this bus to an Atmel development board to read the PMIC registers which also pull-up to 3V3.

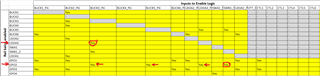

Following things are provided and working fine with PMIC but not able to identify and resolve the power fault,

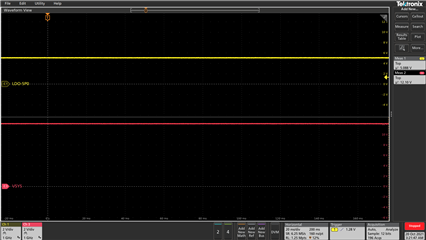

1) VSYS is 12V and is available to PMIC

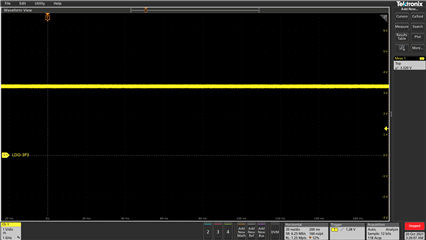

2) LDO3P3/LDO5V0 is available from PMIC

3) Vref 1V3 is available from PMIC

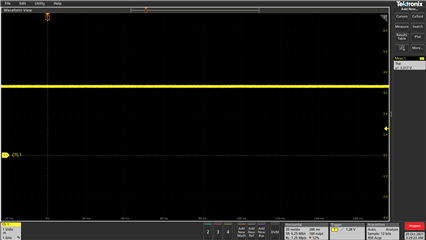

3) CTL1 is provided with LDO3P3

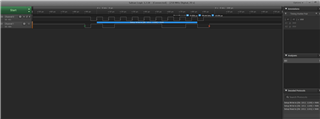

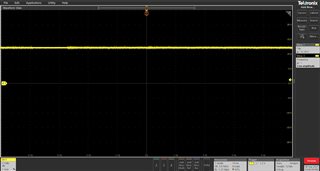

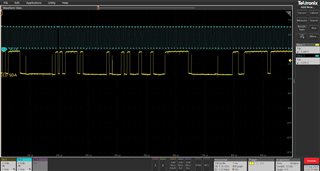

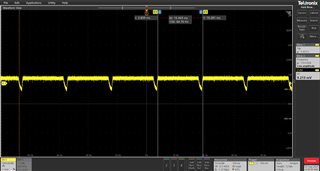

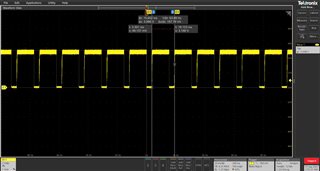

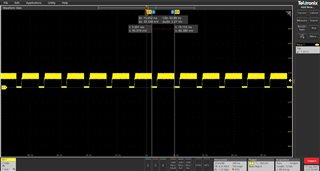

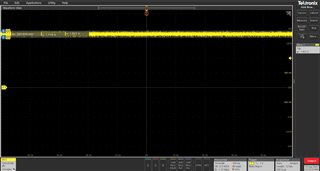

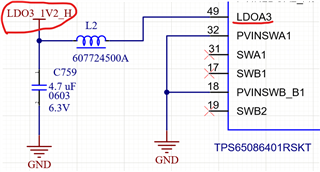

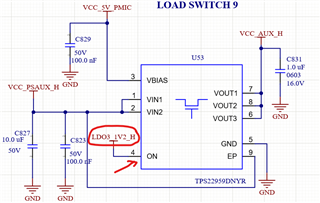

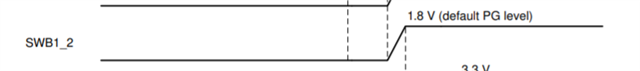

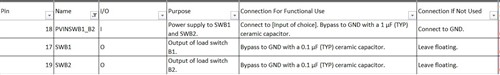

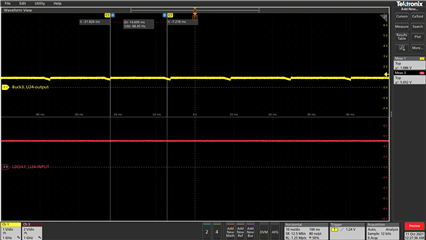

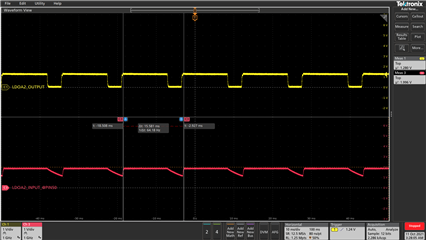

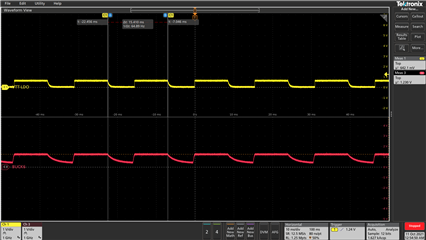

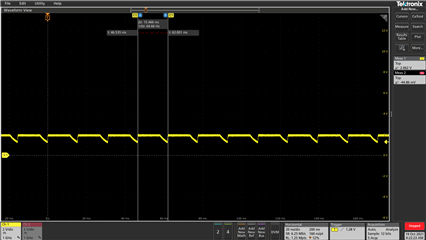

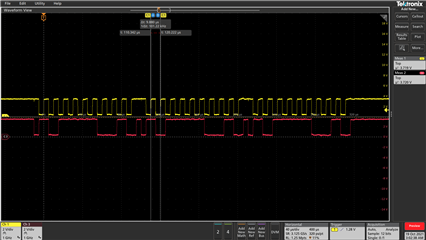

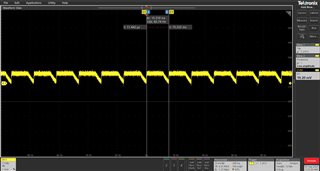

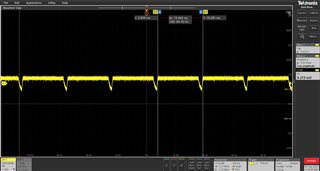

4) Buck1 voltage when reads is at 1V8 but the waveform is as below (Rail, SW, GPO1(+Rail in red))

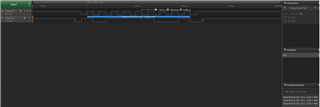

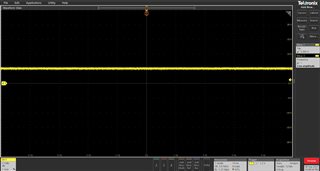

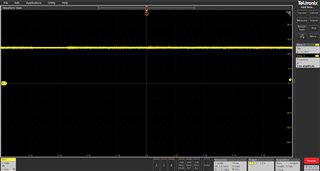

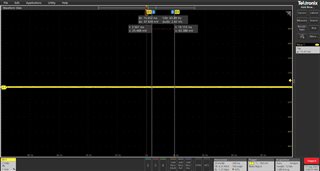

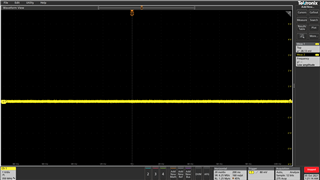

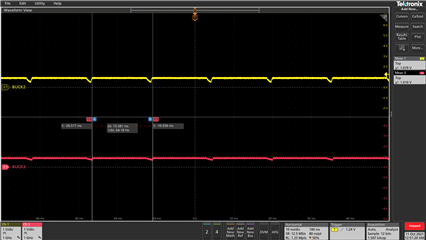

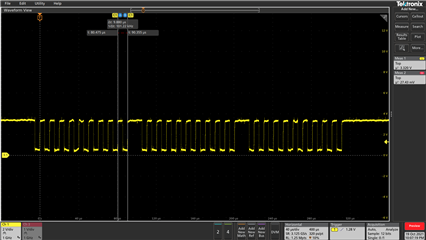

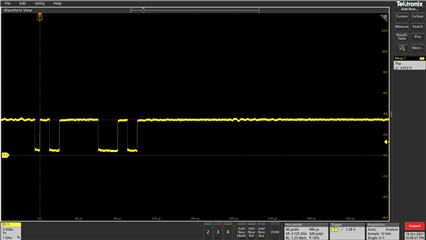

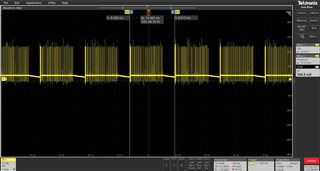

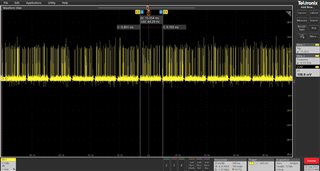

5) Buck2 voltage when reads is at 0V85 but the waveform is as below

After these 2 Bucks there is no outputs from any of the LDO or BUCKS.

I am powering up the board for the first time and doing board bring up task. So could you please help in this regard as i am struggling even to see that I2C itself is not working.

Thanks in advance,

Sandeep P