Hello everyone,

I made a i2c programmable dual voltage supply with 1-12V 5A peak output (typical only 0.5A needed) and input of 5V, or as solder option, 12v in.

Could someone please be so kind and have a look at it?

thank you very much!

sherold

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello everyone,

I made a i2c programmable dual voltage supply with 1-12V 5A peak output (typical only 0.5A needed) and input of 5V, or as solder option, 12v in.

Could someone please be so kind and have a look at it?

thank you very much!

sherold

Hi Stefan,

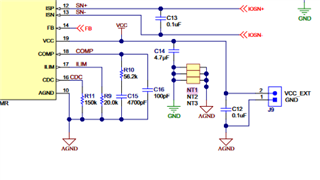

Below are my comments on schematic:

1. I assume when input is 5V, the output peak current is not 5A at 12Vout, right? Otherwise the input current will be 12V*5A/5Vin=12A.

2. Input cap: It's suggested to add one 1uF ceramic capacitor close to VIN pin.

3. MODE pin: A resistor should be put between MODE pin and AGND to configure the device working mode, I2C slave address, VCC source.

4. Output cap: Suggest add two 1uF/0402 package ceramic capacitor close to VOUT pin and PGND pin. Put one in same layer with IC and put another one in opposite layer.

5. Compensation: Suggest add one 100pF ceramic capacitor from COMP pin to AGND.

6. I2C: Please note the I2C needs pull-up resistor to 5V or 3.3V.

Please follow the TPS55288 layout guideline app note.

For some reasons, I cannot see the pads on the gerber file. Could you generate the layout with PDF format? So that I could check the layout.

Thank you alot for your great feedback!

1. correct.

- in case of 5V input an output of 1-5V @ max 2A is the limit.

- in case of 12V input the output limits are 9-12V @5A

2. I did now add another cap (c416/c516), as well there is a spare cap (c504/404) which is a bit fare away but might be usefull as well

3. yes, there already has been such an resistor on another sheet.

4. I plan to assemble all parts only on front layer... C408/C508 (currently marked as "DNP" - but according BOM 2.2uF/0805) should be able to do this job.

5. has been added

6. I know, those pullups have been on another sheet and therefore easy to been overseen

C401/C501 and C410/C510 do have drop in replacements with SMD / THT components so they are interchangeable.

Attached you'll find the modified files in pdf format. Please be aware there are 2 more PCBs merged into you should NOT care about, all components regarding the 2 channel power supply are on the right hand site.

Hi Stefan,

Thanks for the update.

1. OK

2. Yes, put the C416/C516 close to IC pin 3 as decoupling capacitor. Put the C404, C504 close to two external MOSFET to reduce the Buck switching loop switching spikes.

3. Good. But remember to put the MODE pin configuration resistors close to MODE pin.

4. If you can only put all parts on one layer, then suggest you change C408, C508 to 0603 package so that it could be put more close to IC Vout pin and GND pin.

5/6. Good.

Thanks for sharing the pdf file. But could you generate the layout like below picture? So that I can see the silkcreen, IC pads, components pads, PCB trace, copper plane, vias on one picture.

in2_GND.pdffront_GND.pdfbottom_GND.pdfin1_5V.pdf

unfortunatelly I havn't found a setting like you suggested for the front layer. therefore I had to to 2 sheets. every other file does contain a copper layer and the components.

Hi Stefan,

Could you send me the PCB source file? I'll send you the friendship request so that we can discuss it in private.

hhi Zack,

thank you alot for all this great feedback.

Besides one thing I think I could implement everything. But I am still having a hard time understanding the GND+AGND plane separation.

According to the reference schematic there are net ties between GND and AGND. If I understood your last suggestion correct I will end up with separeted nets, not connected at all. is this supposed to be like this? The layout example seems to suggest the same....

but if so why are there net ties? Maybe you could point out where in the layout examples the net ties are placed.

thanks again,

stefan

Hi Stefan,

Both two methods are recommended.

You can follow the EVM design and connect the AGND plane to PGND plane at VCC cap. But you need to take care of pin 9 and pin 11 trace width.

The second method is pouring the AGND pin and PGND pin together on top layer is a easier way. Need to create a AGND plane for VCC cap, COMP, FB network.

Let me know if you have more questions. Thank you.