Other Parts Discussed in Thread: , BQ76942

Hi

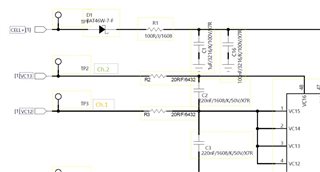

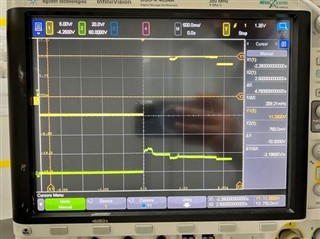

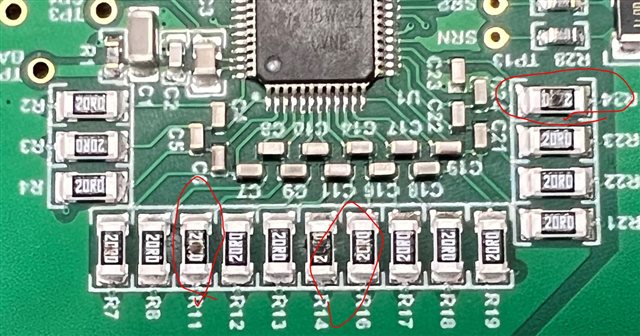

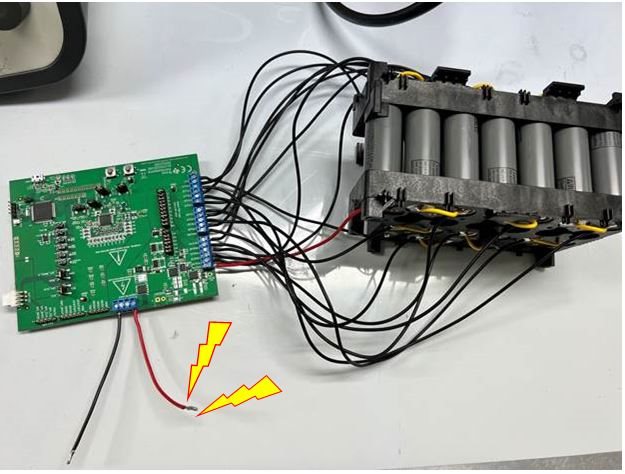

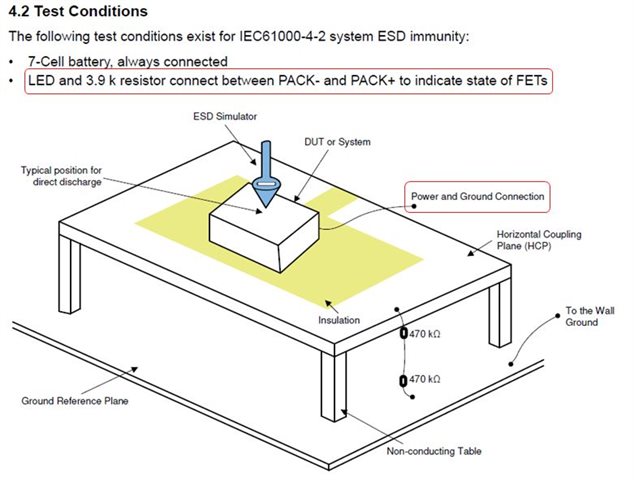

It is said that my customer keeps failing in the esd test.

ESD : Contact ±8~10KV

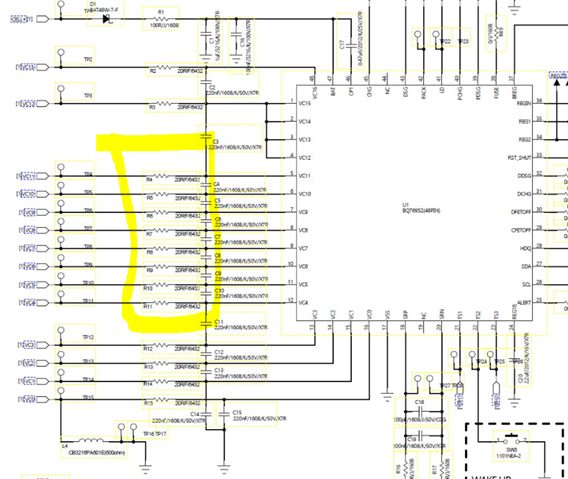

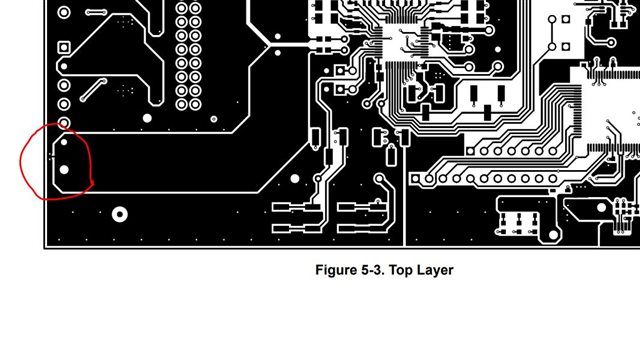

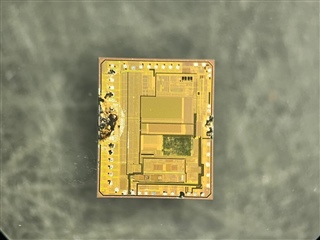

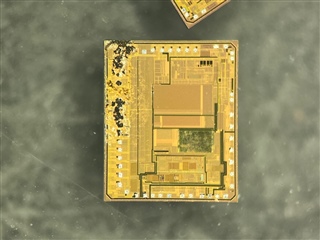

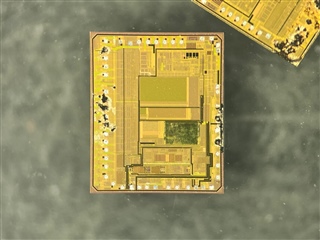

Fail point: bq76952 or

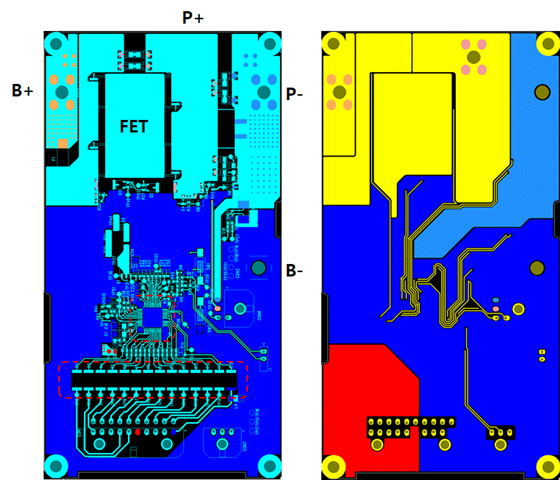

Is there anything to guide about? For example, PCB correction, circuit correction, etc..

Let me know if you have any related information.

Thanks