Other Parts Discussed in Thread: UCC28951

Hi, E2E.

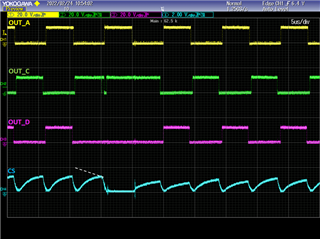

When the current limit works near the maximum duty, the OUT_C and OUT_D of UCC28950 outputs an abnormal waveform.

Can you tell me how to improve this abnormal operation?

DESCRIPTION

OUT_C becomes LOW due to the current limit, but after that (after about 20 ns), it returns to HIGH again for about 500 ns.

As a result, OUT_C turns on longer than usual.

During the next period, OUT_D should be HIGH, but OUT_D remains LOW and the OUTC side becomes HIGH.

Therefore, OUT_C and OUT_D, which should operate alternately, have abnormal outputs.

At this time, OUT_E and OUT_F synchronized with OUT_C and OUT_D also have abnormal outputs.

The OUT_A and OUT_B that synchronize with SYNC are normal.

In a more overloaded condition, the current limit completely limits the duty and returns to normal operation.

By lowering the current limit value or lowering the output voltage set value, it has been confirmed that abnormal operation disappears when the current limit is detected during duty control.

This phenomenon seems to occur when the current limit is detected near the maximum duty.

Regards,

Shimamura.