- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Normally I would take the time to review the DS to help answer this Q, but I am currently resource-strained.

I need to know a summary of all the ways PGOOD works.

1) How the Output Voltage and PGOOD (I am 100% sure this is in the DS)

2) How the EN pin voltage and PGOOD work

Any other ways PGOOD could be triggered High/Low

(Overcurrent, etc)

Regards,

Darren

Hi Darren,

The PG pin is an open-drain output that requires a pull-up resistor to any voltage up to a voltage level of the input voltage at VIN. It can sink 2 mA of current and maintain

its specified logic low level.

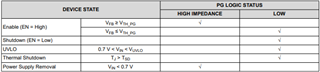

When EN=HI and PG > VTH_PG then PG is high. When EN=HI and PG < VTH_PG then PG is low. PG is low when the device is turned off due to EN, UVLO or thermal shutdown. VIN must remain present (>0.7V) for the PG pin to stay low.

Here is the table summary:

VTH_PG thresholds are mention in EC table:

Hope this helps.

Thanks,

Amod