Other Parts Discussed in Thread: , TPS543B20

Hello,

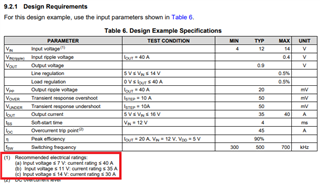

My customer found the current rating recommendations on the TPS543C20 datasheet as below.

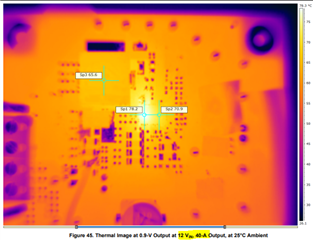

The test results for 40A at 12Vin are also in the datasheet as follows:

Why are there recommended current ratings?

Are these recommendations mandatory for TPS543C20 users to follow?

What problems can be expected if the recommended current rating according to the input voltage is not observed?

Thank you.

JH