Hi Team,

Previously I have already posted a similar thread to enquire about UCC28061(Thread ID: 1105457). I have decided to open another new thread because there is a few more enquiries from my customers.

Could you guide us on the questions below:

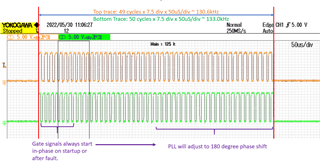

- Why do the two gate outputs work at different frequencies (GDA = 120KHz and GDB = 167.4KHz)?

- Why are the two gates not running 180° out of phase.

- Why are the two gates always turn on at the same time during start up?

- The PFC output can't be regulated at no load. But can be regulated under light load.

- Why are the comp pin unstable at no-load?

- Why the comp pin going high (about 4.9V) for about 400ms after AC off. if ac recycle within 400 mS, then the soft start cannot working.

- How Soft Start Works

- How to set the maximum on duration(Ton-max)?

- How to set the maximum and minimum operating frequency?

Attached is the waveforms for reference.

Thank you very much for your constant support!

Best Regards,

Ernest