Other Parts Discussed in Thread: , UCC21225A, LM5170

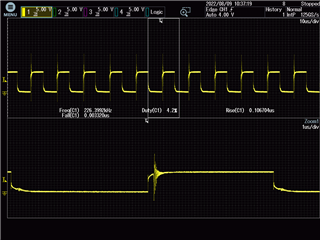

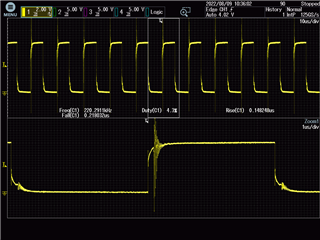

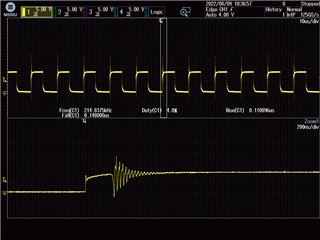

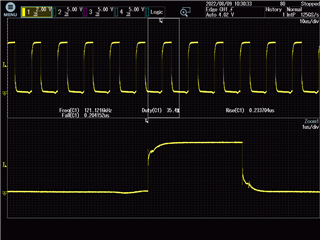

We recently built a two-phase boost circuit using LM5122, with an input of 48V and an output of 96V. However, after each power-on, there will always be a MOS tube that breaks down at the moment of power-on. Where should I investigate this?

mos uses a 200V/100A/11 milliohm, packaged as TO-263;

The circuit design is modified with reference to LM5122EVM-2PH, and the modified circuit switching frequency is 100kHz.