Hi Team,

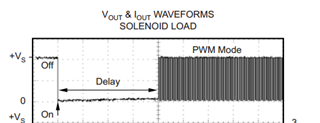

Customer built a Time Delay and relay driver circuit with the DRV103U. The expected result (output) according to the datasheet is this

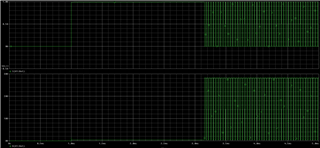

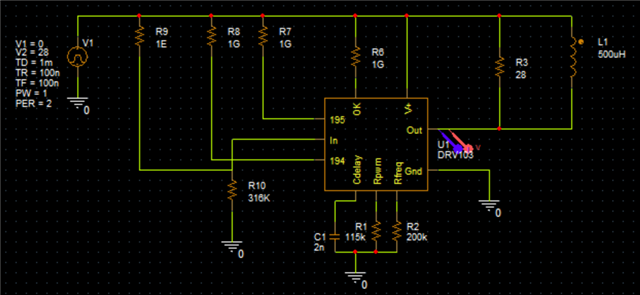

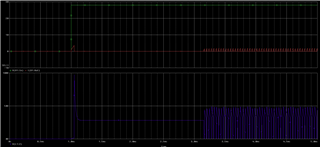

They got this result after simulation

Can you help me to understand why? also can you provide the correct reference for this.

Furthermore, customer sometimes encounter this kind of error when simulation is running "internal error divide by zero" and simulation is aborted. The simulation model that i use id DRV103U in PSpice for TI.

Thank you.

Regards,

May