Other Parts Discussed in Thread: UCC27211

Hi, Team

Our customer use our UCC27211A in their BBU project, our device work's well in normal condition.

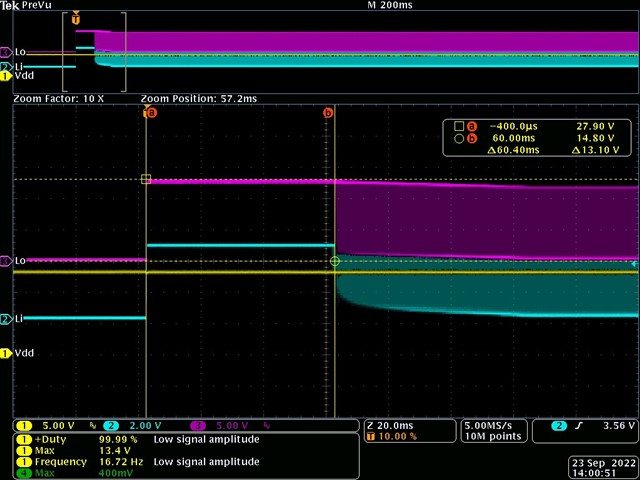

But when they try to permanently Pull Li pin as high , they found that the LO pin will become low.

Does our device have any protection feature to make sure Lo pin will not permanently pull high?

Could u help to give some suggestions?

Thanks.

G.W