Other Parts Discussed in Thread: BQSTUDIO,

Hello Sir:

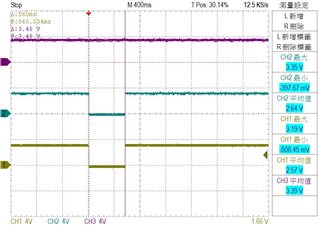

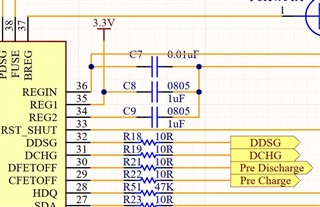

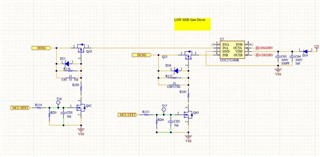

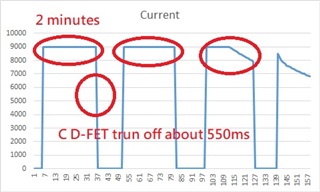

As the title, we set the mosfet on by using ALL_FETS_ON command, but after charging or discharging.

CHG and DSG MOSFET will turn off, but I cannot find reason.

This case happened on MCU firmware, didn't use BqStudio, we log all registers and flash memory for you checking.

Please refer attached files.

If there are not clearly or not enough for checking root cause.

Please let me know which register or flash memory you wanted, I will check back for you.

Looking forward your feedback.

Thanks a lot.

BQ76952_Data_Memory_Table_After_Charge.xlsx

BQ76952_Data_Memory_Table_After_Discharge.xlsx