Other Parts Discussed in Thread: TL431, LM311, LM211, LM211-Q1

Hi Experts,

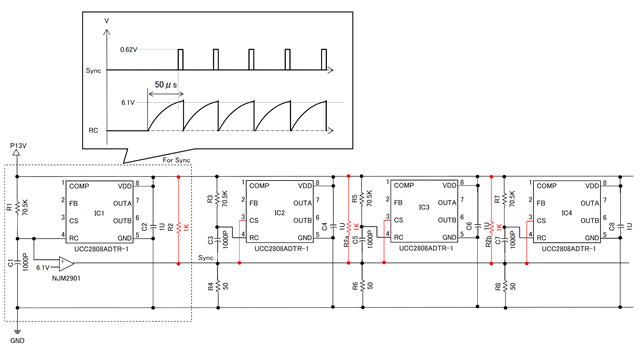

I have two questions about how to use the UCC2808-1.

First, please tell me about the duty ratio adjustment method (circuit).

For example, what kind of circuit design would be used when the duty is 47%?

Second, I want to ground COMP and turn off the outputs (OUTA, OUTB).

Hypothetically, is it a problem to ground COMP for many months with power on?

I hope to receive your advice. Thank you so much.

Kind regards,

Gerald