Dear Sir/Madam,

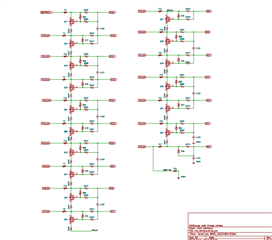

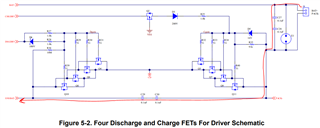

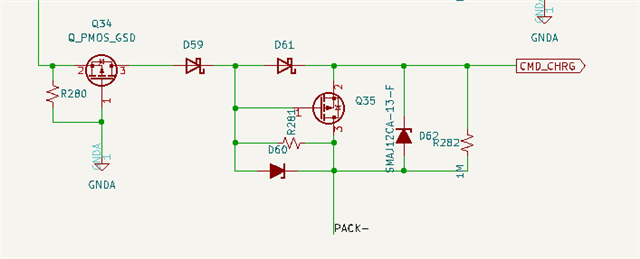

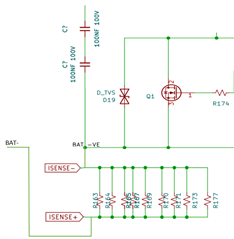

I am working on BMS for Telecom Battery (48 V / 100 Ah ) with 15/16 Cell LFP.

I am using BQ7695202 SPI bms chip with Isolated Communication and try to control from mcu and bms afe using OR gate.

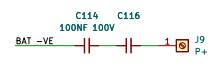

Please check the attached schematic and share your feedback.Let us know to us for any other information