Other Parts Discussed in Thread: TPS51650

Hello,

Greetings of the day!TPS59650RSLT.pdfTPS51650 Calculator DCR Sense_10kNTC QC_Aug1_2011_01_Nov22.xls

I am working on Power Section Design of Intel Atom E3826 using discrete IC's & Components (without PMIC). In the design, two core supplies are required for Atom as follows-

CORE_VCC: 4A @ 1.0V

UNCORE_VNN_S3: 10A @ 1.0V.

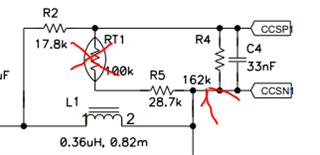

For the above requirement, I am using TPS59650RSLT from TI. This component has 3 CPU phases & 2 GPU phases. And, I have used 1 CPU (for CORE_VCC) & 1 GPU (for UNCORE_VNN). Kindly preview the attached schematic for the reference.

Now, My doubts are-

1) As I am Not using 2 CPU & 1 GPU phases, what should I do with their unused respective pins?

2) Are Bulk capacitors required for the output current 10A & 4A.

3) As I am following Spreadsheet "TPS51650 Calculator DCR Sense_10kNTC QC_Aug1_2011" for the reference, what Inputs should I take for the following sections-

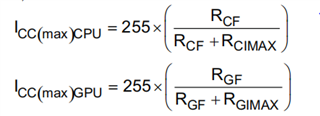

3.A) Thermal Design Current (I_TDC_total)?

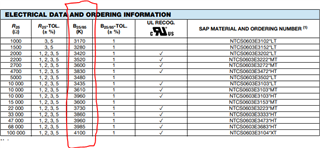

3.B) value of B value of DCR thermal compensation NTC and Resistance of NTC at 25C ?

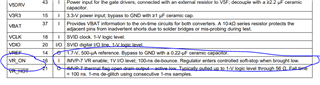

3.C) what is meaning of OSR/USR setting level at COCP-R and GOCP-R that is fixed at 1V & 1.6V?

3.D) IMON voltage at Icc_max?

Please help preview the attached schematic & Design Spreadsheet for the reference-

As, We have on-board space constraint, so please consider use of optimal components while reviewing the design.

Thanks & Regards

Raj Kumar