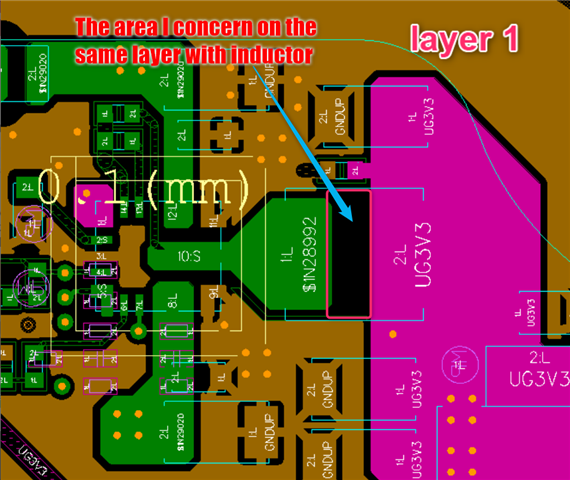

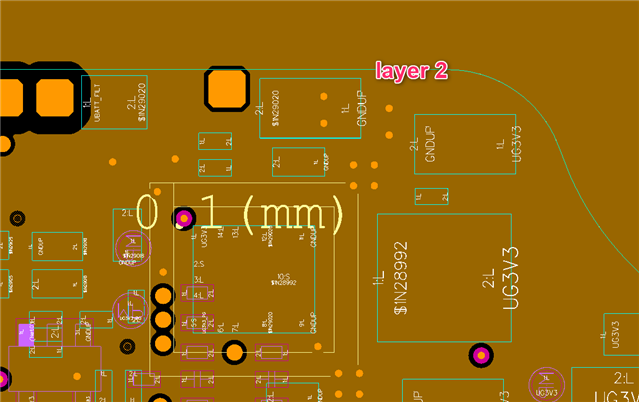

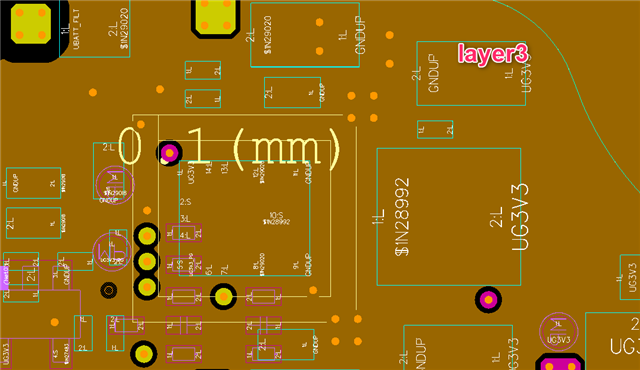

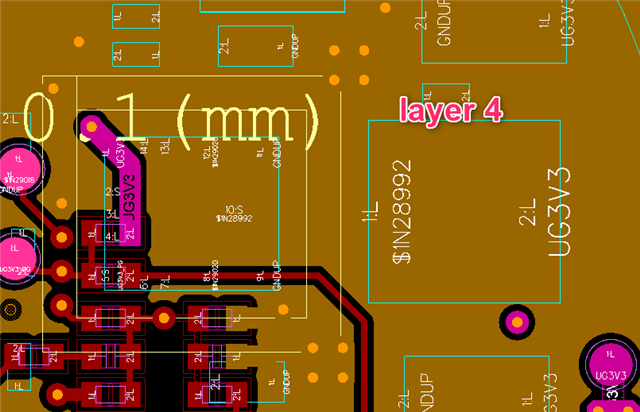

For DC-DC converter design in 4-layer PCB or 6-layer PCB( components on top layer,layer 2 is GND),do we need to remove the GND shape underneath the inductor on the same layer, for good EMC performance?if we don't remove the GND shape ,does it bing in the parasitic capacitance with inductor?

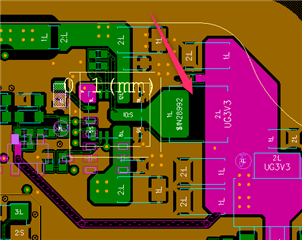

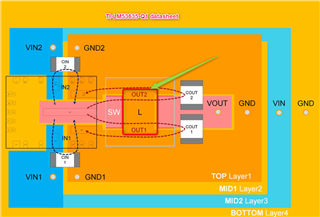

in the layout example of TI-LM53635-Q1 and TI-LM63635-Q1 datasheet, both no keep-out GND design under the inductor. as below

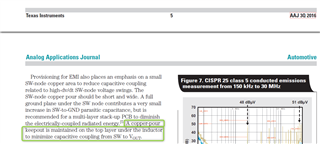

regarding to P6 of "reduce buck-convertor EMI by minimizing inductive parasitics" as below. it recommends set a keep-out area on the top layer under the inductor.FYI

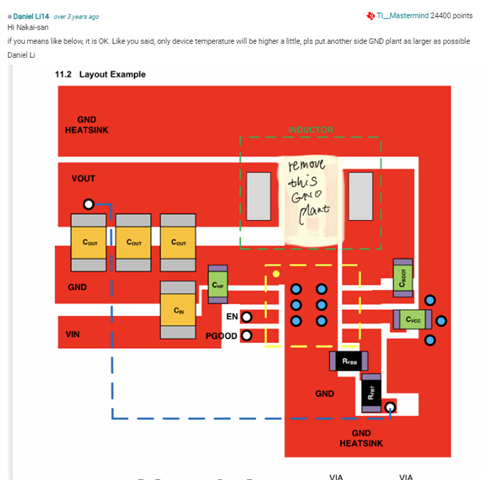

the answer as below link also suggest that design a keep-out area for inductor

I don't know which design is good for EMC performance,and why?Waiting for your advice.Thank you.