Other Parts Discussed in Thread: TPS546D24

Hi team,

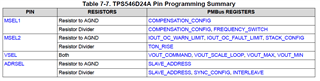

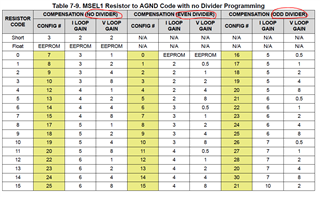

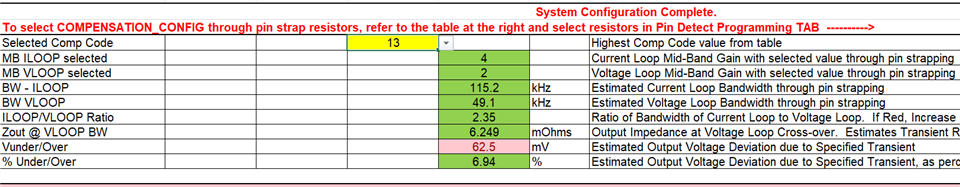

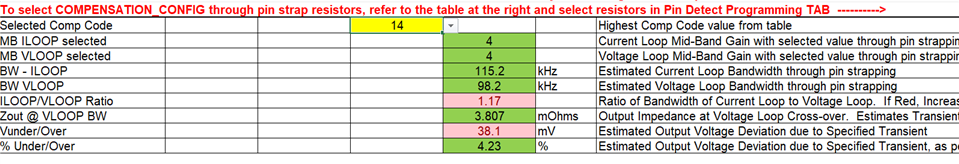

I see a lot of setting is based on resistor code,

but in the datasheet it doesn't mentioned how to choose divided resistor according to each code.

for example what is 0 mean in resistor code?

would you show me ?