Other Parts Discussed in Thread: ATL432, UCC28782, TL431

Hello:

Pl see attached ppt copied from the EVAL kit document.

The table shows how Rdm & Rtz change with load.

How does one interpret the Table?

It is clear that a design is calculated with nominal input & some specific output voltage( min max load) as evidenced by the Spreadsheet Calculator.

A module if built upon these values. Tets are conducted to note vaious characterisrics of the module: expected to satisfy requirements at all "4 corners" as noted in the file.

After this, there is no scope of changing Rdm, Rtz or for that matter ANY value: turns ratio, Rcs, etc..in a delivered functional module...

Does the Table imply that for input/output variations, a fixed design IS NOT OPTIMAL?

Or does it imply that for different input/output ranges, values will be different?.. which is clearly self-evident?

In this latter case, should one not depend upon the results of calculations from the Spreadsheet?

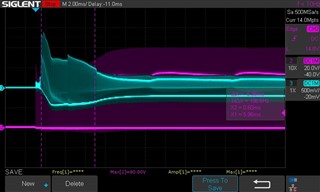

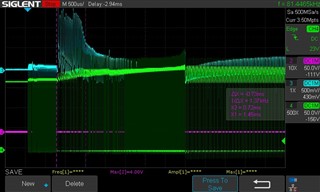

Our search is to find which values of Rdm, Rtz, Rvs1, Rvs2, Rcs, Rsws, Csw and Ropp will not cause failures due to mode transitions as load changes, or during transitions to/from ZVS.

Our design is all GaN based. All components are close to 1% TOL, so the only variants are Vin and Load.

Appreciate any light you can throw on this issue of "optimization" that would have inherent stability in this wider sense to a design.

-r