Hello!

I would like some insight in the interrupt registers and signal(s) on the TPS65988.

First of all, according to the answer @ https://e2e.ti.com/support/interface-group/interface/f/interface-forum/777183/tps65988-tps65988-irq-question

- to get the interrupts currently active from, say Port 1 (address 0x20 lets say), I read register 0x14 (IntEvent1) from address 0x20, and I do not have to "care about IntEvent2"?

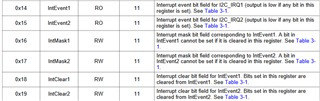

What I am actually wondering is the distinction between IntEvent1, IntMask1, IntClear1, IntEvent2, IntMask2 and IntClear2 - what does the 1 and 2 mean and how do they interact with the I2C2_IRQ signal (pin 34)?

(From Technical Reference Manual)

The reason I have this question is that:

When an interrupt occurs (lets say PlugInsertOrRemoval) on Port 2, the I2C2_IRQ signal (pin 34) goes low/active - as it should, and I can read the IntEvent2 register and see that the PlugInserOrRemoval interrupt is active, handle it and then write the corresponding bit to IntClear2 to clear it (and the I2C2_IRQ signal goes high/inactive).

However, when replicating the same thing on Port 1, the I2C2_IRQ signal never "goes low", but when reading the IntEvent1 register I can see the expected interrupt being active, and writing the corresponding bit high to IntClear1 clears it from IntEvent1.

(Same mask is written to both IntMask1 on 0x20 and IntMask2 on 0x24.)

Thanks for any help in resolving issue.