Other Parts Discussed in Thread: EV2400,

Dear Expert

1.Use the SMBus packet capture tool to capture abnormal packets.

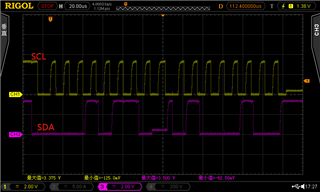

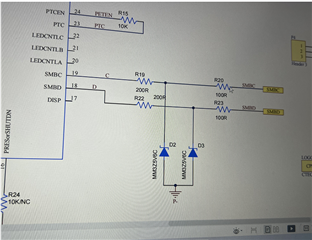

Do charge and discharge simulation test for defective products, when the screen appears "!" When there is an exception, the SMBus packet capture tool is used to capture the abnormal data packets. After analysis, it is found that the BMS does not respond to the answer signal, resulting in the DC board thinking that the BMS is abnormal. No ACK data as shown in the figure below. See the attachment for detailed data.

In the figure below, on the ninth CLK, DATA does not respond to the host by being pulled down by the BMS.

2.Use the TI EV2400 was used to capture BMS data packets separately to observe the accuracy of data packets.

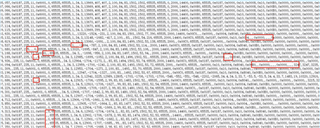

Remove the 3pin line between defective BMS and DC board, use EV2400 directly to capture the BMS data packet, set the time to read the data once a second and save it to the specified file.

Capture the data is to charge and discharge the product at the same time, and find that defective products occasionally appear data errors