The answer was late. sorry

- Is this part of a multi-phase stack or a stand-alone single phase application? Stand-alone single phase is applied.

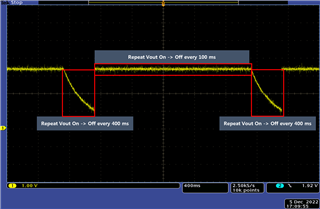

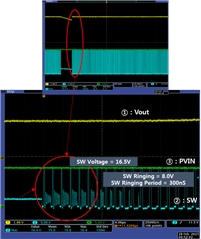

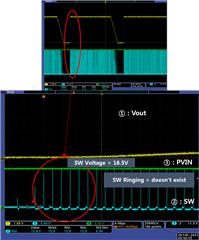

[Question] If Vout is On in [01H] Operation before complete discharge, the ringing phenomenon of SW Pin occurs.

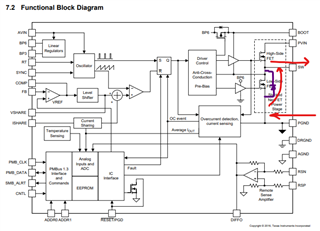

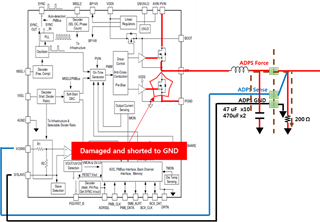

Could it be a device problem (Low FET Damaged and shorted to GND)?

[Refer to] If Vout is turned on in [01H] Operation after complete discharge, there is no ringing phenomenon of SW Pin. (SOFT_OFF Enable)

Thanks for the help i look forward to your answer