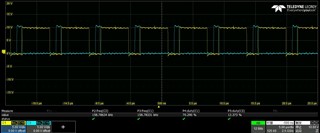

I find the example code of UCD3138HSFBEVM029 EVM firmware . Use Frontend 2 ramp module do SR soft on. Set the RAMPDACEND.RAMP_DAC_VALUE to 1100 according to EVM firmware. The pwm mode is normal . But i find that the SR duty can not above 70%. And the DPWMA duty is only 12%. So i want to know that how to set the RAMPDACEND.RAMP_DAC_VALUE. What does this value relate to? Thanks!

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.