Other Parts Discussed in Thread: LP5912, TPS746-Q1, TPS745-Q1, TPS746

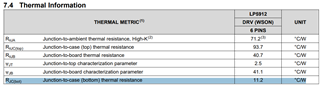

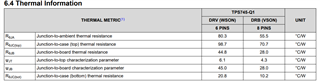

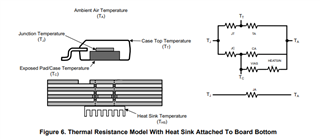

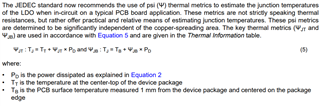

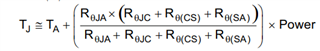

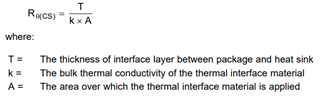

Previously I was able to get information regarding the Junction to Pad thermal resistance for TPS7533QPWP from the HiRel Packaging and Reliability group. We are now looking at a new design considering part LP5912-1.0DRVR, TPS74510PQWDRBRQ1 or TPS74610PQWDRBRQ1 with similar PowePad. I am hoping to also get Junction to Pad thermal resistance for these parts in order to more accurately evaluate the junction temperature in my application. The data sheets only provide junction to case or junction to board information that I do not believe would accurately reflect heat flow through the PowerPad to the board. Use of Theta Junction to Board and Theta Junction to Case results in significant delta temperature between board and case for a device with a PowerPad connection between the two. Our board is also bonded to a heatsink so I believe this would be the primary path of heat flow.

Thank you.