Hello Teams,

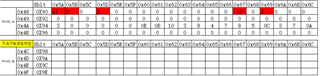

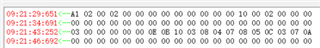

Recently, when our product was running at low temperature, TPS65941212 would have a problem of protective shutdown after running at -40℃ for several hours. After this problem occurred, we read the fault register of TPS6594 as shown in the following table:

From the test table, we can see that the voltage of BUCK3 is under voltage protection, which leads to the output shutdown of TPS6594 .The detailed register values read are shown in the following table

For this problem, can you provide some relevant technical support?

THANKS and wait fot your reply!

.